Классификация Скилликорна

В 1989 году была сделана очередная попытка расширить классификацию Флинна и, тем самым, преодолеть ее недостатки. Д.Скилликорн разработал подход [6], пригодный для описания свойств многопроцессорных систем и некоторых нетрадиционных архитектур, в частности dataflow и reduction machine.

Предлагается рассматривать архитектуру любого компьютера, как абстрактную структуру, состоящую из четырех компонент:

- процессор команд (IP - Instruction Processor) - функциональное устройство, работающее, как интерпретатор команд; в системе, вообще говоря, может отсутствовать;

- процессор данных (DP - Data Processor) - функциональное устройство, работающее как преобразователь данных, в соответствии с арифметическими операциями;

- иерархия памяти (IM - Instruction Memory, DM - Data Memory) - запоминающее устройство, в котором хранятся данные и команды, пересылаемые между процессорами;

- переключатель - абстрактное устройство, обеспечивающее связь между процессорами и памятью.

Функции процессора команд во многом схожи с функциями устройств управления последовательных машин и, согласно Д.Скилликорну, сводятся к следующим:

- на основе своего состояния и полученной от DP информации IP определяет адрес команды, которая будет выполняться следующей;

- осуществляет доступ к IM для выборки команды;

- получает и декодирует выбранную команду;

- сообщает DP команду, которую надо выполнить;

- определяет адреса операндов и посылает их в DP;

- получает от DP информацию о результате выполнения команды.

Функции процессора данных делают его , во многом, похожим на арифметическое устройство традиционных процессоров:

- DP получает от IP команду, которую надо выполнить;

- получает от IP адреса операндов;

- выбирает операнды из DM;

- выполняет команду;

- запоминает результат в DM;

- возвращает в IP информацию о состоянии после выполнения команды.

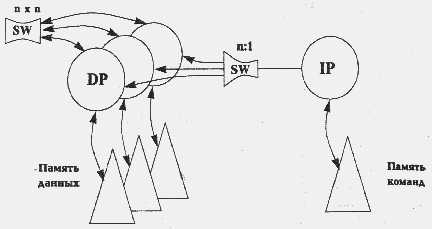

В терминах таким образом определенных основных частей компьютера структуру традиционной фон-неймановской архитектуры можно представить в следующем виде:

Это один из самых простых видов архитектуры, не содержащих переключателей. Для описания параллельных вычислительных систем автор зафиксировал четыре типа переключателей, без какой-либо явной связи с типом устройств, которые они соединяют:

- 1-1 - переключатель такого типа связывает пару функциональных устройств;

- n-n - переключатель связывает i-е устройство из одного множества устройств с i-м устройством из другого множества, т.е. фиксирует попарную связь;

- 1-n - переключатель соединяет одно выделенное устройство со всеми функциональными устройствами из некоторого набора;

- nxn - каждое функциональное устройство одного множества может быть связано с любым устройством другого множества, и наоборот.

Примеров подобных переключателей можно привести очень много. Так, все матричные процессоры имеют переключатель типа 1-n для связи единственного процессора команд со всеми процессорами данных. В компьютерах семейства Connection Machine каждый процессор данных имеет свою локальную память, следовательно, связь будет описываться как n-n. В тоже время, каждый процессор команд может связаться с любым другим процессором, поэтому данная связь будет описана как nxn.

Классификация Д.Скилликорна состоит из двух уровней. На первом уровне она проводится на основе восьми характеристик:

- количество процессоров команд (IP);

- число запоминающих устройств (модулей памяти) команд (IM);

- тип переключателя между IP и IM;

- количество процессоров данных (DP);

- число запоминающих устройств (модулей памяти) данных (DM);

- тип переключателя между DP и DM;

- тип переключателя между IP и DP;

- тип переключателя между DP и DP.

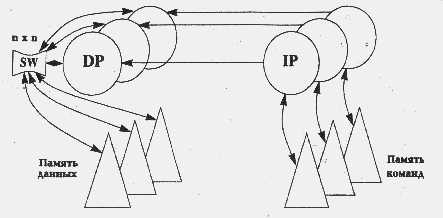

Рассмотрим упомянутый выше компьютер Connection Machine 2. В терминах данных характеристик его можно описать:

(1, 1, 1-1, n, n, n-n, 1-n, nxn),

а условное изображение архитектуры приведено на следующем рисунке:

Для сильно связанных мультипроцессоров (BBN Butterfly, C.mmp) ситуация иная. Такие системы состоят из множества процессоров, соединенных с модулями памяти с помощью динамического переключателя. Задержка при доступе любого процессора к любому модулю памяти примерно одинакова. Связь и синхронизация между процессорами осуществляется через общие (разделяемые) переменные. Описание таких машин в рамках данной классификации выглядит так:

(n, n, n-n, n, n, nxn, n-n, нет),

а саму архитектуру можно изобразить так, как на следующем рисунке:

Используя введенные характеристики и предполагая, что рассмотрение количественных характеристик можно ограничить только тремя возможными вариантами значений: 0, 1 и n (т.е. больше одного), можно получить 28 классов архитектур.

В классах 1-5 находятся компьютеры типа dataflow и reduction, не имеющие процессоров команд в обычном понимании этого слова. Класс 6 это классическая фон-неймановская последовательная машина. Все разновидности матричных процессоров содержатся в классах 7-10. Классы 11 и 12 отвечают компьютерам типа MISD классификации Флинна и на настоящий момент, по мнению автора, пусты. Классы с 13-го по 28-й занимают всесозможные варианты мультипроцессоров, причем в 13-20 классах находятся машины с достаточно привычной архитектурой, в то время, как архитектура классов 21-28 пока выглядит экзотично.

На втором уровне классификации Д.Скилликорн просто уточняет описание, сделанное на первом уровне, добавляя возможность конвейерной обработки в процессорах команд и данных.

В конце данного описания имеет смысл привести сформулированные автором три цели, которым должна служить хорошо построенная классификация:

- облегчать понимание того, что достигнуто на сегодняшний день в области архитектур вычислительных систем, и какие архитектуры имеют лучшие перспективы в будущем;

- подсказывать новые пути организации архитектур - речь идет о тех классах, которые в настоящее время по разным причинам пусты;

- показывать, за счет каких структурных особенностей достигается увеличение производительности различных вычислительных систем; с этой точки зрения, классификация может служить моделью для анализа производительности.

© Лаборатория Параллельных информационных технологий НИВЦ МГУ