Процессор AMD EPYC

Долганов А. М.,

ВМК МГУ,

Москва, 2018

1.Введение

Epyc – серия микропроцессоров компании AMD, нацеленных на использование в серверах и центрах обработки данных. Первое поколение чипов построено на микроархитектуре Zen с использованием нескольких процессорных комплексов, связанных шиной Infinity Fabric.

Все модели Epyc имеют поддержку восьмиканальной DDR4-памяти с частотой до 2666 МГц и 128 линий PCI Express, предназначенных для расширения возможностей системы: подключения вычислительных ускорителей на базе GPU, быстрых хранилищ данных и т. п.), а также специализированные интегрированные ядра для функций, связанных с вопросами безопасности. Обеспечено безопасное шифрование памяти (Secure Memory Encryption - SME) и безопасная шифрованная виртуализация (Secure Encrypted Virtualization – SEV). SME обеспечивает полное шифрование памяти, хранимой в DRAM, а SEV позволяет разным виртуальным машинам иметь свой собственный уникальный ключ шифрования, и таким образом – полностью их изолировать друг от друга, а также от гипервизора операционной системы и от уровня администратора. Эти функции основаны на связанном с контроллером памяти аппаратном процессоре шифрования, где применяется 128-битное шифрование AES[1].

2.Архитектура

Zen — кодовое название микроархитектуры вычислительных ядер процессоров компании AMD, выполненных по технической норме 14 нанометров. На основе этой микроархитектуры вышли процессоры AMD под торговыми марками Ryzen и EPYC.

По словам AMD, основное внимание уделялось увеличению количества операций за такт (IPC, Instructions Per Clock). Переход от микроархитектуры модулей, используемой в Bulldozer, к полноценным ядрам, как ожидалось, поможет увеличить производительность на ядро в операциях с плавающей точкой за счёт большего количества блоков FPU[2].

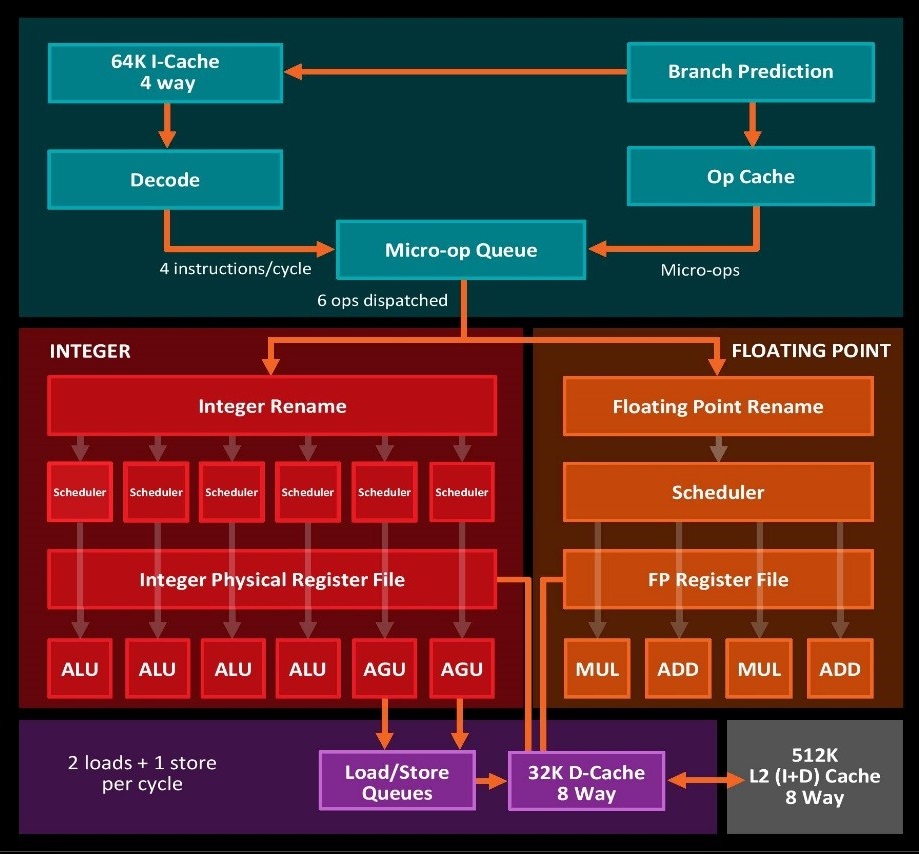

Рисунок 1. Архитектура Zen

Особенности микроархитектуры:

- два потока на ядро

- снижение числа ошибок прогнозирования: совершенствованный предсказатель ветвлений позволяет использовать 2 ветвления в каждом целевом буфере ветвления, но в случае помеченных инструкций будет проходить фильтрация через кэш микроопераций.

- кэш декодированных микроопераций

- увеличенный объём кэш-памяти и оптимизация задержек доступа к ней по 8 МБ общей кэш-памяти третьего уровня типа victim на каждый комплекс из 4 ядер,

- по 512 КБ индивидуальной в 2 раза более быстрой кэш-памяти второго уровня на каждое ядро (включает кэш первого уровня),

- по 64 КБ на инструкции и 32 КБ на данные в индивидуальной в два раза более быстрой кэш-памяти первого уровня на каждое ядро (включён в кэш второго уровня);

- два блока с реализацией аппаратных ускорителей стандарта шифрования AES (Advanced Encryption Standard)[3].

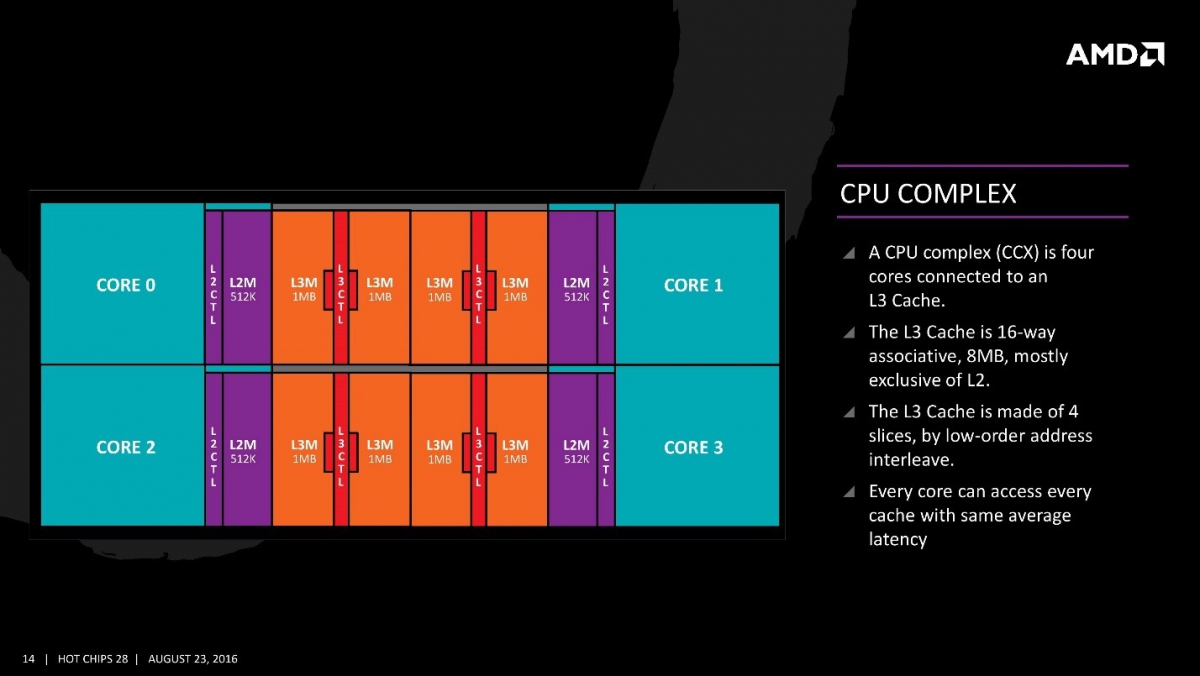

Рисунок 2. CCX

Ядра Zen входят в комплексы, называемые CCX (CPU complex). В каждом CCX обычно расположены 4 ядра Zen с общим для всех ядер кэшем третьего уровня, объёмом 8 МБ на комплекс. Кэш третьего уровня по большей части эксклюзивный, в то время как данные кэша первого уровня обязательно присутствуют в кэше второго уровня. Каждое ядро в комплексе может обратиться к ячейкам кэша любого уровня примерно с одной и той же скоростью, однако в рамках CCX имеется некоторое замедление при обращении к дальней 4МБ половине L3 кэша, а доступ к 8 МБ L3 памяти в соседний CCX проходит с почти на порядок более низкой скоростью. В качестве транзисторов для ядра Zen используются FinFET (Fin Field-effect transistor – полевой транзистор Fin) 14нм[4].

3. Характеристики

В новую линейку процессоров для ЦОД входят модели CPU, включающие от 8 до 32 ядер Zen с поддержкой от 16 до 64 вычислительных потоков. Базовые частоты серверных процессоров AMD находятся в рамках 2,0-2,4 ГГц, а турбо-частоты — от 2,7 до 3,2 ГГц. Уровень TDP (thermal design power) для них установлен в 155 Вт или больше (но не выше 180 Вт для самых мощных решений), и из стройного ряда выбивается только младшая модель Epyc 7251 с восемью ядрами и относительно низким TDP на уровне 120 Вт.

Хотя в семейство процессоров Epyc входят решения с разным количеством ядер, все они поддерживают 128 линий PCIe и восемь каналов DDR4-памяти с рабочей частотой до 2666 МГц и максимальным поддерживаемым объемом ОЗУ в 2 ТБ на процессор. В каждый канал памяти можно устанавливать по два модуля памяти, поэтому максимальный объем поддерживаемой памяти составляет 2 ТБ в однопроцессорной системе и 4 ТБ — в системе с двумя процессорными разъемами.

Разные уровни TDP для большинства моделей зависят от частоты DDR4-памяти и скорости шины Infinity Fabric. Верхний предел TDP указан для использования самой скоростной памяти DDR4-2666, а низкий уровень в 155 Вт будет соответствовать менее скоростным модулям памяти. Все модели, включая младшие, включают поддержку восьми каналов DDR4-памяти, работающих со скоростью до 2666 МГц, так и 128 линий PCI-E[5].

4.Шина Infinity Fabric

Infinity Fabric состоит из двух основных элементов: масштабируемой управляющей структуры и масштабируемой структуры данных. Управляющая структура содержит блоки управления с небольшими удаленными блоками, размещенными в разных модулях SoC[6] (System-on-a-Chip). Масштабируемая структура данных оснащена общей шиной с низкими задержками и когерентной шиной Hyper Transport Plus, многопроцессорной и многокомпонентной. Infinity Fabric — главный элемент Epyc, который используется для соединения четырех 8-ядерных кристаллов на одной подложке, также он связывает и процессорные разъемы.

Все ядра каждого из пары процессоров Epyc 7000 в двухпроцессорной системе связаны друг с другом при помощи Infinity Fabric. Соединения между ядрами полностью когерентны в пределах сокета и оптимизированы для низких задержек и малого энергопотребления. Пропускная способность каждой из двунаправленных связей между ядрами на кристалле равна 42 ГБ/с, что в общем составляет 170 ГБ/с. Двунаправленные каналы между сокетами обеспечивают пропускную способность до 38 ГБ/с и в общем до 152 ГБ/с.

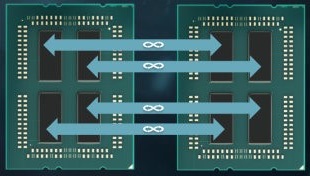

Рисунок 3. Infinity Fabric

Каждое ядро внутри кристалла подключено к каждому из других трех собственным каналом, и каждый кристалл в CPU подключен к аналогичному кристаллу в другом процессорном разъеме, поэтому между любыми из восьми кристаллов двухпроцессорной системы есть связь при помощи одного (если ядра в пределах сокета) или двух каналов — внутреннего и внешнего. Такое решение дополнительно увеличивает задержки при связи между разными вычислительными ядрами (напомним, что восьмиядерный кристалл Zen уже и так состоит из пары четырехъядерных модулей CCX), но в AMD утверждают, что максимально оптимизировали связи для снижения задержек — но это можно проверить только опытным путем[7].

5.Использование

Процессоры AMD Epyc находят применение в облачных решениях, аналитике больших объемов данных, задачах искусственного интеллекта и т.д. В настоящее время существует несколько кластеров высокопроизводительных вычислений с установленными EPYC первого поколения, однако на сегодняшний день в списке TOP500 нет ни одного суперкомпьютера EPYC, исключая систему Advanced Computing System (PreE) от Sugon. Она использует процессоры Dhyana, которые являются лицензионной реализацией EPYC 7501.

Единственное, чего не хватало в EPYC первого поколения, это большое количество флопов, по крайней мере, относительно масштабируемого процессора Intel Skylake Xeon. Топовые чипы Skylake предлагают около 2 терафлопс пиковой производительности, в то время как соответствующие процессоры AMD EPYC обеспечивают менее половины этого[8].

6.Ссылки

https://www.ixbt.com/cpu/amd-epyc-launch.shtml

https://www.amd.com/ru/products/epyc

https://www.xelent.ru/blog/funktsii-bezopasnosti-v-amd-epyc/

https://www.top500.org/news/amd-notches-epyc-supercomputer-win-with-next-generation-zen-processor/

[3] https://www.anandtech.com/print/10591/amd-zen-microarchiture-part-2-extracting-instructionlevel-parallelism

[5] https://www.anandtech.com/print/10591/amd-zen-microarchiture-part-2-extracting-instructionlevel-parallelism

[6] Электронная схема, выполняющая функции целого устройства и размещённая на одной интегральной схеме.