#### U.A. Каляев $^1$ , U.И. Левин $^1$ , E.A. Семерников $^2$

<sup>1</sup>НИИ многопроцессорных вычислительных систем имени академика А.В. Каляева Южного федерального университета, г. Таганрог, Россия; <sup>2</sup>Южный научный центр РАН, г. Ростов-на-Дону, Россия

# АРХИТЕКТУРА СЕМЕЙСТВА РЕКОНФИГУРИРУЕМЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ НА ОСНОВЕ ПЛИС

В статье приводятся описание архитектуры и принципов построения семейства реконфигурируемых вычислительных систем с динамически перестраиваемой архитектурой на основе ПЛИС производительностью до 6 Тфлопс, создаваемого в рамках Федеральной целевой программы «Исследования и разработки по приоритетным направлениям развития научно-технологического комплекса России на 2007-2012 годы». В качестве основного вычислительного элемента в них используются не универсальные микропроцессоры, а программируемые логические интегральные схемы сверхбольшой интеграции. Все представители семейства предназначены для решения вычислительно трудоемких задач различных предметных областей, обеспечивают реальную производительность не ниже 50% от пиковой производительности на широком классе задач и имеют практически линейный рост производительности при наращивании аппаратного ресурса.

#### Введение

В настоящее время наибольшее распространение в мире получили суперЭВМ кластерного типа. Это связано, прежде всего, с удобством программирования, а также с тем, что они строятся из комплектующих на основе универсальных микропроцессоров, обладающих высокой технологичностью и относительно низкой стоимостью. В то же время пользователи отмечают принципиальные недостатки кластерных суперЭВМ, которые заключаются в существенном снижении их производительности при решении многих практических задач. Так, например, высокую реальную производительность кластерные суперЭВМ демонстрируют, в основном, только при решении класса слабосвязанных задач, не требующих большого числа информационных обменов, в то время как при решении задач других классов их реальная производительность существенно снижается и не превышает 5-10% от декларируемой пиковой производительности системы. Это является следствием неадекватности конкретной архитектуры суперкомпьютера информационной структуре решаемой задачи [1, 2, 3].

Недостатки кластерных систем, связанные с их неизменной «жесткой» архитектурой, позволяет преодолеть концепция создания реконфигурируемых вычислительных систем (РВС) с «гибкой», динамически перестраиваемой (программируемой) архитектурой [3-5,7,9]. Концепция создания РВС разработана в Научно-исследовательском институте многопроцессорных вычислительных систем имени академика А.В. Каляева Южного федерального университета (НИИ МВС ЮФУ) и развивается уже более 20 лет. В отличие от многопроцессорных вычислительных систем с «жесткой» архитектурой архитектура РВС может

динамически изменяться в процессе функционирования. В результате у пользователя появляется возможность адаптации архитектуры вычислительной системы под структуру решаемой задачи. Иными словами, пользователь может, оставаясь в рамках базовой архитектуры системы, создавать проблемно-ориентированные вычислители, структура которых соответствует структуре решаемой задачи. Проведенные исследования и многочисленные практические разработки, выполненные в НИИ МВС ЮФУ, показали [4-9], что реализация данной концепции обеспечивает высокую реальную производительность РВС, близкую к пиковой, на широком классе задач, в том числе при решении «сильносвязанных» задач.

## Принципы организации вычислений в РВС

В отличие от традиционных методов организации параллельных вычислений РВС ориентируются на абсолютно параллельную форму алгоритма задачи – ее информационный граф. Под информационным графом [2] понимается граф, соответствуют арифметико-логическим операциям вершины которого операндами или ячейками (каналами) памяти, которых расположены информационные массивы. Дуги информационного графа соответствуют информационной зависимости между вершинами. Если существует направленная дуга, соединяющая вершину a с вершиной b, то это означает, что результат операции, соответствующий вершине информационного графа a, является входным операндом операции, соответствующей вершине b. Вершины, соответствующие каналам памяти, в которых располагается входная и выходная информация, являются входными И выходными вершинами информационного Информационные графы больших и сложных задач могут содержать миллионы вершин.

Идея концепции построения РВС заключается в аппаратной реализации всех операций, предписанных вершинами информационного графа задачи, всех каналов передачи данных между вершинами, соответствующих дугам графа, и всех информационных каналов, соответствующих входным и выходным вершинам. В этом случае задача, определенная информационным графом, будет выполнена максимально быстро, поскольку обеспечивается максимально возможное распараллеливание вычислений. Такое решение задачи принято называть структурным [4,5].

Очевидно, что информационные графы больших задач не могут быть целиком имеющемся аппаратном pecypce PBC. ЭТОМ случае информационный граф большой сегментируется на фрагменты задачи непересекающиеся базовые подграфы, физически реализуемые в аппаратуре РВС, а решение большой задачи выполняется структурно-процедурным способом, при котором на аппаратный ресурс РВС поочередно отображаются базовые подграфы информационного графа, и вычисления в соответствии с отображенным подграфом выполняются структурно, а смена подграфов выполняется процедурно [4, 5, 7, 8].

В простейшем случае структурно-процедурный вычислительный процесс в РВС организуется следующим образом. В аппаратном ресурсе РВС реализуется один из базовых подграфов сегментированного информационного графа задачи и на его входы из блоков памяти подаются входные данные этого фрагмента. Процесс вычисления реализуется вычислительной структурой, соответствующей данному подграфу, и на выходе формируется результат вычислений, который запоминается в

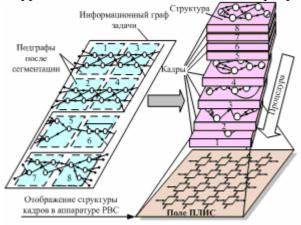

соответствующих блоках памяти. Далее в аппаратном ресурсе РВС реализуется следующий базовый подграф сегментированного информационного графа задачи, и процесс повторяется. Этот процесс показан на рис. 1.

При реализации структурно-процедурного метода информационный граф задачи представляется в виде кортежа изоморфных базовых подграфов, которые являются информационно-независимыми или непосредственно зависящими друг от друга. Кортеж информационных подграфов преобразуется в специальную вычислительную конструкцию - кадр. Можно сказать, что кадру соответствует подграф задачи, реализованный аппаратно, через который следует поток операндов. При этом каждая группа операндов (результатов) соответствует входным (выходным) вершинам определенного подграфа кортежа. Смена кадров в РВС осуществляется процедурно по единой для всей системы программе.

Рис. 1. Процесс решения задачи в РВС

Механизм последовательного обхода подграфов информационного графа задачи кадрами принято называть *структурно-процедурной организацией вычислений*.

РВС со структурно-процедурной организацией вычислений является гибридом фон-неймановской архитектуры и архитектуры потока данных. Такая организация вычислений обеспечивает детерминизм выполнения программы, что в общем случае недостижимо в многопроцессорных системах, построенных по традиционной мультипроцедурной архитектуре (кластерные МВС). При этом обеспечивается также и высокая эффективность параллельных вычислений на широком классе задач.

## Архитектура РВС

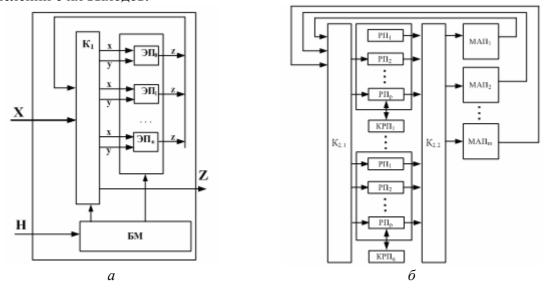

Основными вычислительными блоками в РВС являются макропроцессоры (МАП). Макропроцессор позволяет реализовывать крупные операции, которые предписаны вершинами информационного графа. Макропроцессор представляет собой некоторый набор элементарных процессоров (ЭП), объединяемых в единый вычислительный программно-неделимый pecypc c помощью локального пространственного коммутатора  $(K_1)$  (рис. 2, a). Внутренний коммутатор макропроцессора, как правило, соединяет по полному графу все информационные входы и выходы элементарных процессоров, внешние информационные входы X,

внешние информационные выходы Z макропроцессора. Настройка макропроцессора на крупную функционально законченную операцию (макрооперацию) производится с помощью блока макроопераций (БМ). В каждый момент времени макропроцессор может реализовывать только одну макрооперацию. Незадействованные в макрооперации элементарные процессоры будут простаивать.

Следует отметить, что в отличие от стандартного микропроцессора элементарный процессор макропроцессора не управляет процессом обработки информации, а лишь реализует соответствующую ему операцию над операндами, поступающими на его входы.

Для реализации того или иного информационного графа решаемой задачи макропроцессоры должны иметь возможности соединения в вычислительные параллельно-конвейерные структуры. С этой целью в состав РВС включен коммутатор второго уровня или системный коммутатор, обеспечивающий различные варианты соединения макропроцессоров друг с другом. В состав РВС входит также распределенная память, обеспечивающая возможности параллельной выдачи массивов входных данных на входы макропроцессоров и записи результатов вычислений с их выходов.

Рис.2. Структурная схема макропроцессора a и обобщенная схема РВС  $\delta$

Обобщенная схема РВС приведена на рис. 2 б. В ее состав входят множество макропроцессоров, состоящих из элементарных процессоров, соединяемых между собой с помощью локального коммутатора; множество каналов распределенной памяти (РП), в каждый из которых входит контроллер распределенной памяти (КРП), а также системный коммутатор  $K_2$ , предназначенный как для соединения макропроцессоров с друг с другом в вычислительные структуры, так и для их параллельного доступа к каналам распределенной памяти. Множество входных и выходных дуг информационного графа реализуется системным коммутатором  $K_2$ , обеспечивающим подключение каналов распределенной памяти к тем или иным входам и выходам макропроцессоров. При этом массивы входных данных отображаются в соответствующие каналы распределенной памяти, процедура обращения к которым реализуется с помощью КРП.

Особенность архитектуры РВС заключаются в том, что в процессе конструирования она не формируется окончательно, а остается в определенном смысле незавершенной и открытой. Окончательное программирование архитектуры РВС включает создание функциональных узлов (элементарных процессоров) для выполнения вычислений, настройку прямых информационных коммутаторах  $K_1$  и  $K_2$  между элементарными процессорами, настройку блоков распределенной памяти на реализацию процедур чтения и записи информационных Аппаратно-программные средства РВС позволяют синтезировать произвольные соединения между компонентами системы, создавая необходимые вычислительные структуры. Совокупность вычислительных структур, созданных в архитектуры PBC, образуют виртуальный рамках базовой проблемноориентированный вычислитель, структура которого адекватна информационному графу (подграфу) решаемой задачи.

Реализация и широкое внедрение в практику концепции высокопроизводительных РВС требуют соответствующей элементной базы, удовлетворяющей следующим основным критериям:

- высокой степени интеграции, позволяющей реализовать крупные фрагменты вычислений;

- сравнительно низкой стоимости при мелкосерийном производстве вычислительных систем;

- возможности аппаратной реализации специализированных вычислительных структур;

- возможности реализации различных схем распараллеливания вычислений;

- возможности реконфигурации сформированных вычислительных структур при переходе от одних алгоритмов и схем распараллеливания к другим;

- поддержки разработки схемотехнических решений системами автоматизированного проектирования.

Всем этим требованиям отвечают появившиеся в конце XX-го и начале XXI-го века программируемые логические интегральные схемы (ПЛИС) со сверхвысокой степенью интеграции (в английской аббревиатуре FPGA – Filed Programmable Gates Array). В ПЛИС изначально заложены возможности реконфигурирования их внутренней архитектуры, и поэтому они наилучшим образом соответствуют концепции реконфигурируемых вычислительных систем.

Применение ПЛИС большой степени интеграции дало возможность перейти к созданию в РВС больших решающих полей, содержащих множество однотипных микросхем. При этом функциональные узлы и вычислительные блоки, реализуемые в решающем поле, могут не привязываться к конкретным микросхемам, поскольку в любом месте решающего поля могут быть реализованы любые функциональные устройства, которые необходимы в данном месте. В этом смысле решающее поле является как бы аналогом сверхбольшой ПЛИС, объединяющим ресурсы всех микросхем.

Однако построение больших решающих полей на ПЛИС требует преодоления некоторых проблем. Одна из них - это негативный эффект границ, возникающих на стыках отдельных ПЛИС при их объединении в решающее поле. Эффекты границ сказываются при реализации больших фрагментов вычислительных структур, которые не могут быть реализованы в пределах отдельной микросхемы, а требуют ресурса нескольких ПЛИС. Вторая проблема - это конструктивно-технологические ограничения, которые заключаются в том, что невозможно разместить

неограниченное количество ПЛИС на печатной плате приемлемого размера. Эта проблема решается путем модульного построения аппаратных средств РВС и модульной наращиваемости на основе унифицированных базовых модулей. Базовые модули не только позволяют путем комплексирования создавать РВС необходимой производительности, но и сами по себе являются реконфигурируемой вычислительной системой, способной совместно с персональным компьютером (в качестве интеллектуального терминала) решать пользовательские задачи.

Введение модульного принципа построения аппаратных средств обостряет первую проблему, порождая еще один тип границ – межмодульный. Как будет показано ниже, суть решения проблемы границ заключается в создании единого типа интерфейса как между ПЛИС в пределах базового модуля, так и между ПЛИС разных базовых модулей.

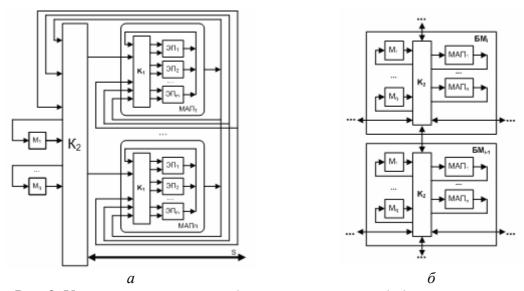

Архитектурные особенности базового модуля и модульно наращиваемой PBC на его основе показаны на рис. 3a и  $3\delta$  соответственно.

Рис. 3. Укрупненная структура базового модуля a и обобщенная структура модульно-наращиваемой РВС  $\delta$

В состав базового модуля входит некоторое множество макропроцессоров (МАП) и блоков памяти (М), объединенных с помощью пространственной коммутационной системы  $K_2$ . Каждый макропроцессор, в свою очередь, содержит m элементарных процессоров (ЭП), объединенных коммутатором  $K_1$ . Таким образом, в базовом модуле, показанном на рис. 3a, имеет место двухуровневая коммутационная система. Первый уровень устанавливает связи между элементарными процессорами внутри макропроцессора, а второй уровень — связи между макропроцессорами внутри базового модуля. Наращивание производительности РВС достигается путем объединения нескольких базовых модулей в единый вычислительный ресурс. Пример объединения базовых модулей с использованием для этого возможностей коммутатора  $K_2$  показан на рис. 36.

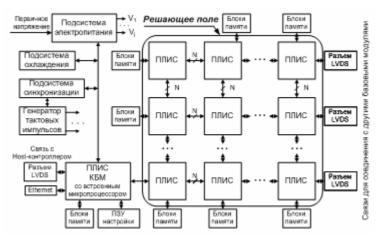

На рис. 4 показана типовая структура базового модуля на основе ПЛИС, который несет в себе все характерные признаки завершенной РВС [4-7].

Рис. 4. Структура базового модуля реконфигурируемой системы на основе ПЛИС

Основные вычислительные возможности базового модуля сосредоточены в решающем поле, которое содержит некоторое множество ПЛИС большой степени интеграции. В решающем поле создаются вычислительные и коммутационные структуры: макропроцессоры  $MA\Pi_{I} - MA\Pi_{n}$ , каждый из которых, в свою очередь, содержит несколько элементарных процессоров  $\Im \Pi_{I} - \Im \Pi_{m}$ , объединенных коммутаторами  $K_1$ , внутримодульный коммутатор  $K_2$ , контроллеры распределенной памяти для управления блоками распределенной памяти. При этом сами блоки распределенной памяти выполняются на типовых микросхемах ОЗУ SRAM или SDRAM необходимого объема и быстродействия. Контроллер базового модуля (КБМ) выполняет функции управления и контроля всех систем базового модуля. На модуле располагаются также И вспомогательные подсистемы: синхронизации, электропитания и охлаждения.

ПЛИС решающего поля располагаются в узлах двумерной решетки и соединяются между собой ортогональной системой связей по близкодействию. Такая система связей позволяет существенно упростить печатную плату и улучшить ее частотные характеристики, поскольку связи между соседними микросхемами не превышают единицы сантиметров. Данные между дальними микросхемами передаются по транзитным каналам через промежуточные микросхемы, используя систему ортогональных связей.

Центральное место в организации вычислительного процесса отводится распределенной Контроллеры памяти контроллерам памяти. работают фрагментами параллельной программы, которые загружены в их блоки памяти. Исполняя параллельную программу, контроллеры распределенной участвуют в настройке элементарных процессоров на выполнение необходимых операций и создают с помощью коммутаторов  $K_1$  и  $K_2$  необходимые каналы связи между ними, тем самым реализуя в пределах базового модуля мультиконвейерную вычислительную структуру, соответствующую базовому подграфу задачи.

Одна часть контроллеров распределенной памяти, исполняя фрагменты параллельной программы, организует и синхронизирует потоки данных, подаваемые в вычислительные структуры. Другая часть контроллеров выполняет функции приема результатов вычислений. Базовый модуль с точки зрения организации

потоков данных через аппаратно реализованный в нем базовый подграф показан на

рис. 5.

Рис. 5. Организации потоков данных через аппаратно реализованный базовый подграф

Для создания эффективных вычислительных структур в пределах базового модуля необходимо оптимальное соотношение количества ПЛИС, количества блоков распределенной памяти и их объема. Для различных задач, решаемых на РВС, это соотношение различно. В то же время для структурной реализации вычислений не требуется запоминание множества промежуточных данных, так как они передаются для дальнейшей обработки в последующие ступени конвейерного вычислителя без промежуточного запоминания. Это снижает требования к общему объему памяти на базовом модуле. Для структурной реализации вычислений более критичным является количество блоков распределенной памяти, а не объем каждого блока или общий объем памяти. Помимо распределенной памяти, реализованной на типовых микросхемах ОЗУ, при создании вычислительных структур широко используется внутрикристальная память ПЛИС.

Поскольку в решающем поле реализуются вычислительные структуры, которые располагаются в ресурсах нескольких или даже всех микросхем, то необходимо стремиться к тому, чтобы максимально снизить негативный эффект границ между кристаллами ПЛИС. Снижение межкристального эффекта границ достигается двумя путями. Первый из них предполагает использование ПЛИС максимальной интеграции, которые позволяют размещать все более крупные фрагменты функциональных узлов. Второй путь заключается в создании регулярных и однородных связей между всеми ПЛИС базового модуля и всей РВС в целом.

С этой целью связи между ПЛИС решающего поля базового модуля целесообразно выполнять на основе стандарта LVDS (Low Voltage Differential Signaling –дифференциальные сигналы низкого напряжения). Преимуществами стандарта LVDS являются: низкая потребляемая мощность выходных каскадов, низкий уровень создаваемых электромагнитных излучений, невосприимчивость к синфазным электромагнитным помехам и наличие в микросхемах современных ПЛИС аппаратной поддержки для организации высокоскоростных передач данных на основе стандарта LVDS. Темп передачи данных по каждой двухпроводной линии в зависимости от реализации может составлять несколько гигабит в секунду.

Поскольку при реализации вычислительных структур больших базовых подграфов может не хватить ресурсов одного базового модуля, то возникает

необходимость реализации таких структур в пределах двух и более базовых модулей. При этом важно сохранить темп передачи данных из микросхем решающего поля одного базового модуля непосредственно в ПЛИС другого базового модуля. Для сохранения темпа передачи в межмодульных обменах целесообразно также использовать стандарт LVDS. Единый тип интерфейса между ПЛИС как в пределах одного базового модуля, так и между различными базовыми модулями, обеспечивает одинаковые скорости обмена и снижает эффект границ в пределах общего схемотехнического ресурса РВС.

Принцип модульной наращиваемости позволяет увеличить производительность РВС при увеличении количества базовых модулей. При этом обеспечивается возможность организации ресурсонезависимого и отказоустойчивого программирования, параметризуемого относительно вычислительного ресурса (количества базовых модулей), выделяемого для решения задачи. Задача может быть решена на любой конфигурации вычислительной структуры. Выход из строя одного или нескольких базовых модулей не влечет за собой прекращение решения задачи и необходимость ее полной перетрансляции, а лишь несколько замедляет процесс решения [4,5,7].

На основе описанной выше концепции в НИИ МВС ЮФУ за последние 5-6 лет был создан ряд РВС различной производительности и назначения, из которых две системы в настоящее время выпускаются серийно. Показатели «компактности» и «эффективности» созданных систем составили 5-6 Гфлопс/дм $^3$  и менее 18000-20000 руб/Гфлопс. Для задач символьной обработки эти же показатели составили  $115x10^9$  операцй/дм $^3$  и 2000 руб/млрд.оп.

#### Состав семейства РВС

В настоящее время по заданию Федерального агентства по науке и инновациям ведется выполнение Государственного контракта № 02.524.12.4002 по теме «Создание семейства высокопроизводительных многопроцессорных вычислительных систем с динамически перестраиваемой архитектурой на основе реконфигурируемой элементной базы и их математического обеспечения для решения вычислительно трудоемких задач» в рамках Федеральной целевой программы «Исследования и разработки по приоритетным направлениям развития научно-технологического комплекса России на 2007-2012 годы».

Целью разработки является создание на единых архитектурных принципах семейства программно-совместимых РВС производительностью от 0,025 Тфлопс до 6 Тфлопс. Создаваемое семейство РВС включает:

- PBC-5 высокопроизводительную систему производительностью 6 Тфлопс;

- РВС-1Р и РВС-1К системы производительностью более 1 Тфлопс;

- РВС-0.2-РС рабочую станцию производительностью 300 ГФлопс;

- РУПК-50 и РУПК-25 ускорители персональных компьютеров производительностью 50 и 25 ГФлопс.

Старшие представители семейства создаются на принципах модульной наращиваемости на основе вычислительного блока PBC-0.2-ВБ и базового модуля 16V5-75 и обладают почти линейным ростом реальной производительности в зависимости от увеличения аппаратного ресурса [4,5,7,8].

a 6

Внешний вид вычислительного блока и базового модуля 16V5-75 производительностью более 300 Гфлопс и 75 Гфлопс соответственно, из которых строятся старшие представители семейства РВС, показаны на рис. 6.

Рис.6. Вычислительный блок PBC-0.2-BБ – a и базовый модуль  $16V5-75-\delta$

Для создания семейства PBC, системного и прикладного программного обеспечения его представителей, информационной и программной инфраструктуры для обучения и поддержки потенциальных пользователей семейства образован консорциум из ряда научных и научно-производственных организаций, в который вошли: НИИ МВС ЮФУ (г. Таганрог) — головной исполнитель проекта; ФГУП «НИИ «Квант» (г. Москва); «Южный научный центр РАН» (г. Ростов-на-Дону); «Специальная астрофизическая обсерватория РАН» (пос. Нижний Архыз); НИЦ «СуперЭВМ и нейрокомпьютеров» (г. Таганрог); НИВЦ МГУ (г. Москва).

Реальная производительность всех представителей семейства РВС планируется не ниже 50% от указанной пиковой производительности на широком классе вычислительных задач. При этом они будут обладать существенно меньшими габаритами, энергопотреблением и стоимостью по сравнению с суперЭВМ кластерного типа аналогичной производительности.

## Системное программное обеспечение

Программирование РВС отличается от программирования МВС традиционной архитектуры, и его можно условно разделить на две составляющие: программирование структурное, которое создает необходимые вычислительные структуры в поле логических ячеек ПЛИС, и программирование процедурное – программирование в традиционном смысле, заключающееся в организации вычислительного процесса в РВС. При этом программирование вычислительных структур вызывает у пользователей наибольшие трудности [4,5,10]. Это связано с тем, что традиционно пользователи привыкли программировать только организацию вычислительного процесса, опираясь на неизменяемую аппаратную поддержку средств вычислительной техники, в то время как для программирования

вычислительных структур РВС требуется совершенно другая квалификация, а именно - квалификация схемотехника.

При программировании пользовательской задачи структура РВС приобретает черты специализированной многопроцессорной ЭВМ, которая соответствует структуре решаемой задачи из предметной области. Это обеспечивает высокую реальную производительность системы, близкую пиковой производительности на широком классе задач, и позволяет достичь практически линейного роста производительности при наращивании аппаратного ресурса. Эффективность вычислительного процесса при реконфигурации архитектуры РВС на низком (схемотехническом) уровне может быть повышена от 10 до 100 раз по сравнению с вычислительными системами, архитектура которых не может быть Это делает, с одной стороны, чрезвычайно привлекательной реконфигурируемые на низком уровне системы, а с другой стороны, их программирование становится по сложности сопоставимым с созданием новой вычислительной системы. Поэтому требуются новые методы и средства создания прикладных параллельных программ для решения прикладных задач на РВС.

Создаваемое в рамках проекта системное и прикладное программное обеспечение обеспечивает потенциальным пользователям удобство программирования сложных практических задач на РВС и включает: программный комплекс средств разработки прикладных программ, средства администрирования вычислительных ресурсов РВС и служебные программы и драйверы.

Программный комплекс средств разработки прикладных программ для PBC, создаваемый в рамках проекта, предоставляет пользователю возможности, которые позволяют создавать программы без привлечения специальных знаний в области схемотехники ПЛИС и по сложности приближены к обычному программированию для многопроцессорных ЭВМ.

#### Заключение

Описанные архитектура построения статье принципы высокопроизводительных систем на основе ПЛИС и создаваемое на этих принципах семейство принципиально новым направлением PBC являются развития высокопроизводительной вычислительной техники. В качестве основного **PBC** вычислительного элемента В используются не универсальные микропроцессоры, а программируемые логические интегральные схемы. Это дает возможность пользователям создавать в базовой архитектуре РВС виртуальные специализированные вычислители, структура которых адекватна структуре решаемой задачи, что, в свою очередь, обеспечивает высокую эффективность вычислений и близкий к линейному рост производительности при наращивании вычислительного ресурса.

Проблема снижения производительности традиционных МВС на сильносвязанных задачах может быть разрешена только путем предоставления пользователю больших возможностей в части архитектурного программирования аппаратного параллелизма вычислительной системы. В этом контексте РВС, построенные на архитектурных принципах, описанных в статье, обладают рядом преимуществ перед многопроцессорными системами традиционной организации,

которые основаны на использовании микропроцессоров в качестве основного вычислительного элемента.

### Литература

- 1 Аладышев О.С., Дикарев Н.И., Овсянников А.П. и др. СуперЭВМ: области применения и требования к производительности Известия ВУЗов. Электроника, 2004. №1. С.13-17.

- 2 Воеводин В.В., Воеводин Вл.В. Параллельные вычисления. С.-Петербург: «БХВ-Петербург», 2002.-599 с..

- 3. Каляев А.В. Многопроцессорные вычислительные системы с программируемой архитектурой. М.: Радио и Связь, 1984. 240 с.

- 4. Каляев А.В., Левин И.И. Модульно-наращиваемые многопроцессорные системы со структурно-процедурной организацией вычислений. М.: Янус-К, 2003. 380 с.

- 5. Каляев И.А., Левин И.И., Семерников Е.А., Шмойлов В.И. Реконфигурируемые мультиконвейерные вычислительные структуры. Ростов н/Д: Издательство ЮНЦ РАН, 2008. 320 с.

- 6. Беседин И.В., Дмитренко Н.Н., Каляев И.А., Левин И.И., Семерников Е.А. Семейство базовых модулей для построения реконфигурируемых многопроцессорных вычислительных систем со структурно-процедурной организацией вычислений // Материалы Всероссийской научной конференции «Научный сервис в сети Интернет: технологии распределенных вычислений», Новороссийск. М.: Издательство Московского университета, 2006. С 47-49.

- 7. Каляев И.А., Левин И.И. Высокопроизводительные модульно-наращиваемые многопроцессорные системы на основе реконфигурируемой элементной базы // Вычислительные методы и программирование. М.: Изд-во Московского Университета, 2007. Т.8. №1. С. 181-190.

- 8. Каляев А.В., Каляев И.А., Левин И.И. Многопроцессорные вычислительные системы с программируемой архитектурой на основе ПЛИС Вестник ЮНЦ РАН, 2004. С.24-33.

- 9. Дордопуло А.И., Каляев И.А., Левин И.И., Семерников Е.А. Семейство многопроцессорных вычислительных систем с динамически перестраиваемой архитектурой // Материалы Четвертой Международной научной молодежной школы «Высокопроизводительные вычислительные системы». Таганрог: Изд-во ТТИ ЮФУ, 2007, 68-74.

- 10. Левин И.И. Язык параллельного программирования высокого уровня для структурнопроцедурной организации вычислений // Труды Всероссийской научной конференции. М.: Изд-во МГУ, 2000, 108-112.