# Onyx2 Reality,<sup>TM</sup> Onyx2 InfiniteReality and Onyx2<sup>TM</sup> InfiniteReality2<sup>TM</sup> Technical Report

Silicon Graphics, Inc.

A description of the functionality and operation of the Onyx2 Reality, Onyx2 InfiniteReality and Onyx2 InfiniteReality2 visualization systems. © 1996 Silicon Graphics, Inc. Printed in the United States of America. 2011 N. Shoreline Boulevard, Mountain View, California 94043

All rights reserved. No part of this work may be reproduced in any form or by any means graphic, electronic, or mechanical, including photocopying, recording, taping, or storage in an information retrieval system—without prior written permission of the copyright owner.

Specifications subject to change without notice.

RESTRICTED RIGHTS LEGEND: Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 (October 1988) and FAR 52.227-19 (June 1987).

The product described in this manual may be protected by one or more U.S. patents, foreign patents, and/or pending applications.

All other products or services mentioned in this document are identified by the trademarks as designated by the companies that market those products or services. Inquiries concerning such trademarks should be made directly to those companies.

| 1.0 | Intro                    | oduction                                                                                                                                                       | 1                                                                                                        |

|-----|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|     | 1.1<br>1.2<br>1.3        |                                                                                                                                                                | 1<br>1<br>2<br>5<br>6<br>6                                                                               |

| 2.0 | Ony                      | x2 Reality and Onyx2 InfiniteReality2 Overview                                                                                                                 | 7                                                                                                        |

| 3.0 | Gra                      | phics APIs                                                                                                                                                     | 9                                                                                                        |

|     | 3.1<br>3.2<br>3.3<br>3.4 | OpenGL <sup>®</sup><br>IRIS Performer<br>OpenGL Optimizer<br>"Fahrenheit"                                                                                      | 9<br>9<br>10<br>11                                                                                       |

| 4.0 | Geo                      | metry Subsystem                                                                                                                                                | 13                                                                                                       |

|     | 4.1                      | Geometry Engine                                                                                                                                                | 13                                                                                                       |

| 5.0 | Ras                      | ter Subsystem                                                                                                                                                  | 14                                                                                                       |

|     | 5.1<br>5.2               | Texture Processing         Pixel Processing                                                                                                                    | 14<br>14                                                                                                 |

| 6.0 | Disp                     | blay Subsystem                                                                                                                                                 | 16                                                                                                       |

|     | 6.1                      | ACCESS.bus                                                                                                                                                     | 17                                                                                                       |

| 7.0 | Gra                      | phics Features and Capabilities                                                                                                                                | 18                                                                                                       |

|     | 7.1<br>7.2<br>7.3<br>7.4 | 7.4.1Shading7.4.2Color Blending7.4.3Lighting7.4.4Advanced Lighting Model7.4.5Surface Properties7.4.6Infinite Light Sources7.4.7Local Light SourcesTransparency | 18<br>20<br>21<br>21<br>22<br>22<br>23<br>23<br>23<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>25<br>25 |

|     | 7.6<br>7.7<br>7.8        | Hidden Surface RemovalCoplanar Geometry PrioritizationAnti-Aliasing7.8.1Sample Memory                                                                          | 25<br>25<br>26<br>27                                                                                     |

|      | 7.8.2   | Onyx2 Reality Restrictions                             | 27 |

|------|---------|--------------------------------------------------------|----|

| 7.9  | Texture | /Image Mapping                                         | 28 |

|      | 7.9.1   | Texture Download                                       | 28 |

|      | 7.9.2   | Texture Formats                                        | 29 |

|      | 7.9.3   | Texture Filtering                                      | 30 |

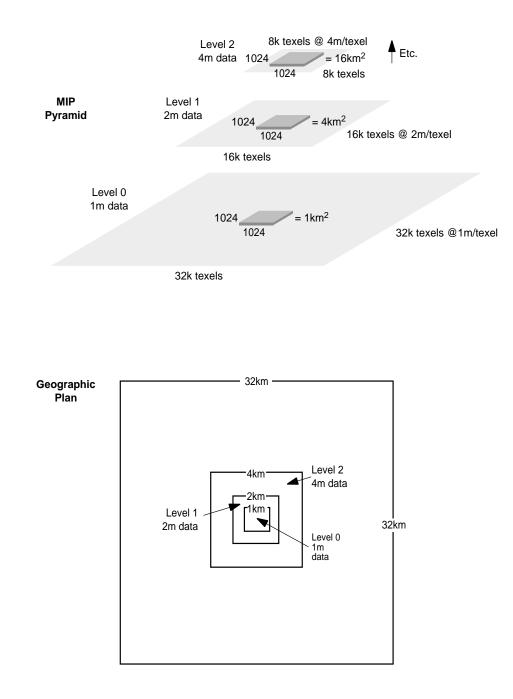

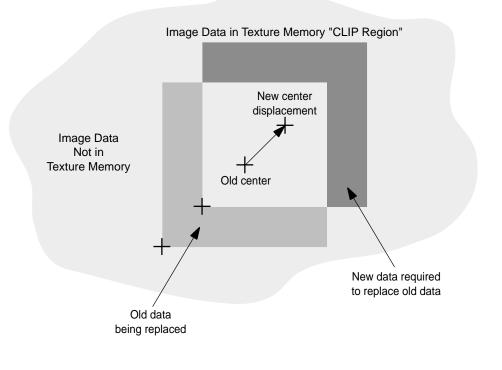

|      | 7.9.4   | Global Texturing a.k.a. CLIP mapping                   | 31 |

|      | 7.9.5   | Add, Replace, Blend, Decal, and Modulation             | 34 |

|      | 7.9.6   | Texture/Image Memory                                   | 34 |

|      | 7.9.7   | Texture Memory Packing                                 | 36 |

|      | 7.9.8   | Texture Transparency and Contouring                    | 36 |

|      | 7.9.9   | Perspective Correction                                 | 36 |

|      | 7.9.10  | Detail Texture                                         | 36 |

|      | 7.9.11  | Sharp Texture                                          | 37 |

|      | 7.9.12  | Projective Texture                                     | 37 |

|      | 7.9.13  | Shadow Maps                                            | 37 |

|      | 7.9.14  | Billboards                                             | 37 |

|      | 7.9.15  | Detail Management                                      | 37 |

|      | 7.9.16  | Video to Texture                                       | 37 |

|      | 7.9.17  | 3D Textures and Volume Rendering                       | 38 |

|      | 7.9.18  | Texture Color Lookup Tables                            | 38 |

| 7.10 | Imaging | g Operations                                           | 38 |

|      | 7.10.1  | Convolution                                            | 38 |

|      | 7.10.2  | Histogram and Minmax                                   | 39 |

|      |         | Color Matrix and Linear Color Space Conversion         | 39 |

|      |         | Window/Level Support                                   | 39 |

|      |         | Lookup Tables (LUTs)                                   | 39 |

| 7.11 |         | oheric Effects                                         | 39 |

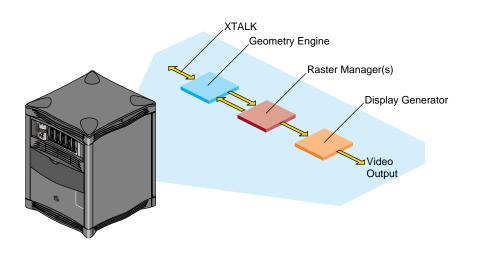

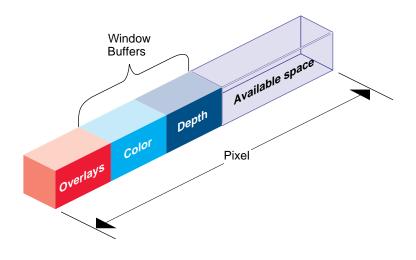

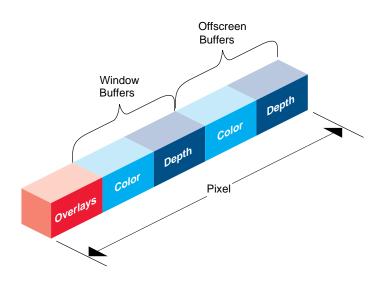

|      |         | en Rendering                                           | 40 |

|      |         | hannel Display Generator                               | 42 |

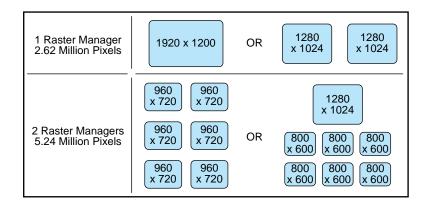

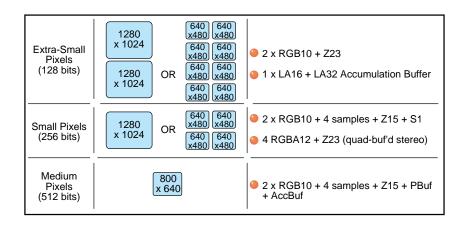

|      | 7.13.1  | Standard Formats and Format Combinations               | 42 |

|      | 7.13.2  | 2-Channel and 8-Channel Configurations                 | 45 |

|      | 7.13.3  | Onyx2 Reality and Onyx2 InfiniteReality2 Multi-Channel |    |

|      |         | Features: Considerations                               | 45 |

|      |         | 7.13.3.1 Swap Rates Must Be Equal                      | 45 |

|      |         | 7.13.3.2 Frame Buffer to Video Display Subsystem       |    |

|      |         | Transmission Bandwidth                                 | 47 |

|      |         | 7.13.3.3 DAC Output Bandwidth                          | 47 |

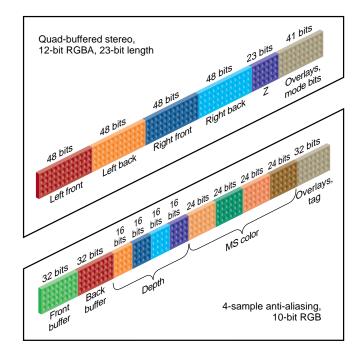

|      |         | 7.13.3.4 Frame Buffer Memory                           | 48 |

|      |         | 7.13.3.5 Frame Buffer Read/Write Bandwidth             | 48 |

|      | 7.13.4  | Video Format Combiner                                  | 48 |

|      | 7.13.5  | Examples of Video Format Combinations                  | 50 |

|      |         | Video Format Compiler                                  | 51 |

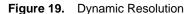

|      | 7.13.7  | Dynamic Resolution                                     | 51 |

|      | 7.13.8  | Stereoscopic Video Output                              | 52 |

|      | 7.13.9  | Direct Support of Color Field Sequential Video         | 52 |

|      | 7.13.10 |                                                        | 52 |

|      | 7.13.11 | Programmable Video Timing                              | 52 |

| 7.14 | Genloc  |                                                        | 53 |

|      | 7.14.1  | Swap Synchronization                                   | 53 |

| 7.15 | Digital | Video Multiplexer - DPLEX                              | 54 |

|      |         |                                                        |    |

|     | 7.17<br>7.18 | 7.15.2<br>7.15.3<br>7.15.4<br>7.15.5<br>Digital V<br>Graphic<br>Integra | Video Option (DIVO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54<br>54<br>55<br>55<br>56<br>56<br>57 |

|-----|--------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

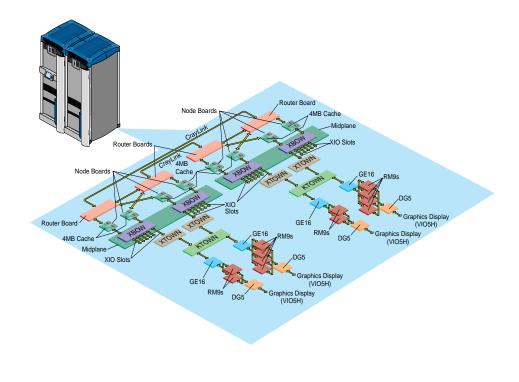

| 8.0 | -            |                                                                         | ware Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                     |

|     | 8.1          |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                     |

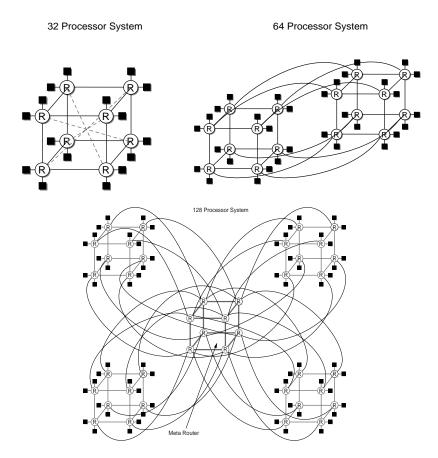

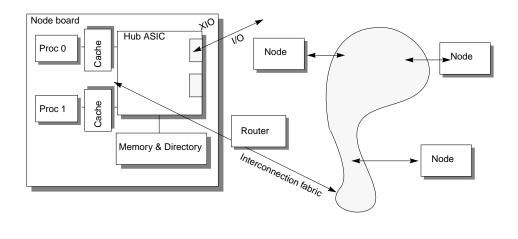

|     | 8.2          | Node C                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59                                     |

|     |              | 8.2.1                                                                   | Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                     |

|     |              | 8.2.2<br>8.2.3                                                          | Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60<br>60                               |

|     |              | o.z.s<br>8.2.4                                                          | Hub   Global Real-Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                     |

|     | 8.3          |                                                                         | osystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                     |

|     | 0.0          | 8.3.1                                                                   | XIO Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                     |

|     |              | 8.3.2                                                                   | XBOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62                                     |

|     |              | 8.3.3                                                                   | XIO Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64                                     |

|     |              | 8.3.4                                                                   | Media Input/Output (MIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64                                     |

|     |              | 8.3.5                                                                   | PCI-64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64                                     |

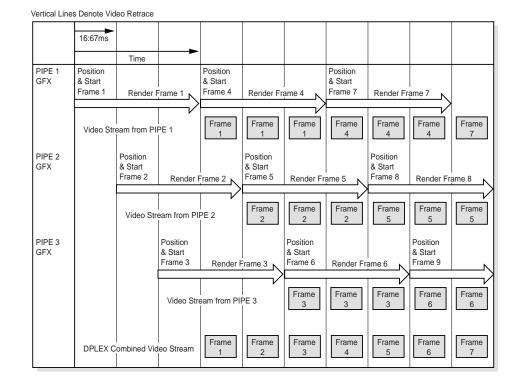

|     | 8.4          | Interco                                                                 | nnect Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65                                     |

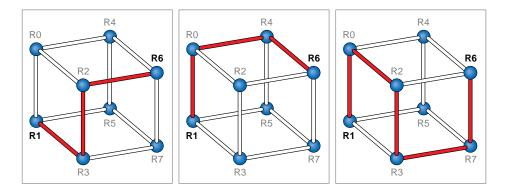

|     |              | 8.4.1                                                                   | Тороюду                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                     |

|     |              | 8.4.2                                                                   | Routers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                                     |

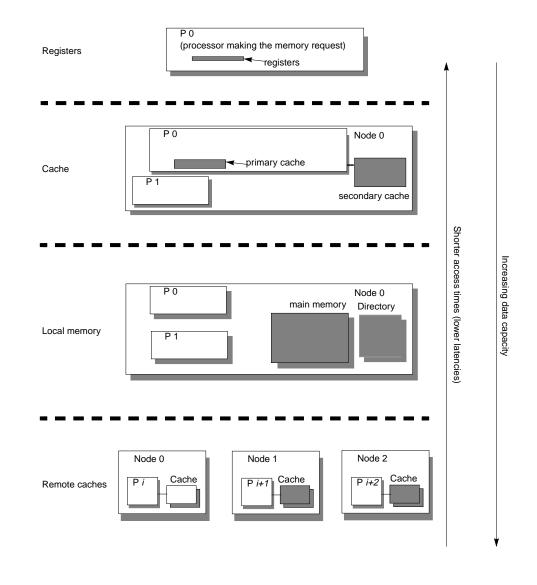

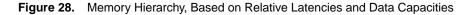

|     | 8.5          |                                                                         | ted Shared Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66                                     |

|     | 8.6          | •                                                                       | Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67                                     |

|     | 8.7<br>。。    |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68<br>69                               |

|     | 8.8<br>8.9   | -                                                                       | a Latencies b Bandwidths b Ban | 69<br>69                               |

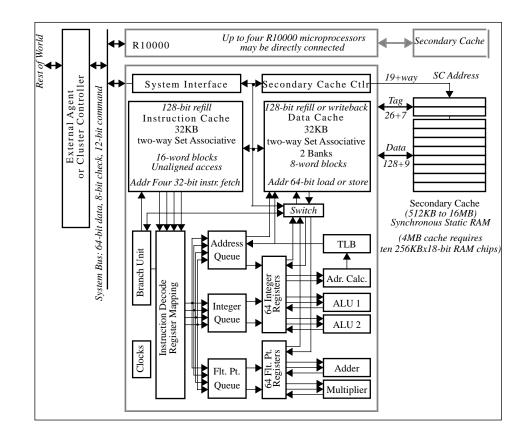

|     |              |                                                                         | ) Processor Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71                                     |

|     | 0.10         |                                                                         | R10000 Product Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72                                     |

|     |              |                                                                         | Primary Data Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73                                     |

|     |              |                                                                         | Secondary Data Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73                                     |

|     |              |                                                                         | Instruction Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                     |

|     |              | 8.10.5                                                                  | Branch Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                     |

|     |              |                                                                         | Queueing Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74                                     |

|     |              |                                                                         | Register Renaming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                     |

|     |              |                                                                         | Execution Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75                                     |

|     |              | 8.10.9                                                                  | Load/Store Units and the TLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75                                     |

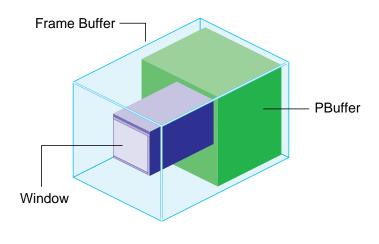

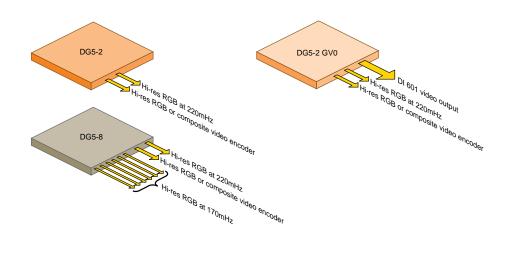

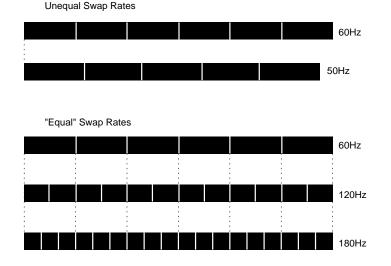

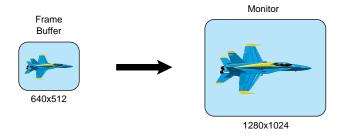

| 9.0 | IRIX         |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76                                     |