# Understanding IBM eserver pSeries Performance and Sizing

ibm.com/redbooks

Redbooks

# International Technical Support Organization

Understanding

IBM @server pSeries

Performance and Sizing

February 2001

| Τs | ike | N | ot. | ا ۵ |

|----|-----|---|-----|-----|

|    |     |   |     |     |

Before using this information and the product it supports, be sure to read the general information in Appendix A, "Special notices" on page 377.

#### Second Edition (February 2001)

This edition applies to IBM RS/6000 and IBM @server pSeries as of December 2000, and Version 4.3.3 of the AIX operating system.

This document was updated on January 24, 2003.

Comments may be addressed to: IBM Corporation, International Technical Support Organization Dept. JN9B Building 003 Internal Zip 2834 11400 Burnet Road Austin, Texas 78758-3493

When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1997, 2001. All rights reserved.

Note to U.S Government Users – Documentation related to restricted rights – Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

# **Contents**

| Preface  The team that wrote this redbook                |      |

|----------------------------------------------------------|------|

| Comments welcome                                         | . 11 |

| Chapter 1. Introduction                                  | 1    |

| Chapter 2. Background                                    |      |

| 2.1 Performance of processors                            |      |

| 2.2 Hardware architectures                               | 6    |

| 2.2.1 RISC/CISC concepts                                 |      |

| 2.2.2 Superscalar architecture: pipeline and parallelism | 7    |

| 2.2.3 Memory management                                  | . 11 |

| 2.2.4 PCI                                                | . 19 |

| 2.2.5 MP implementation specifics                        | 21   |

| 2.2.6 NUMA                                               | . 24 |

| 2.2.7 Logical partitioning (LPAR)                        | 26   |

| 2.3 AIX kernel                                           | . 28 |

| 2.3.1 Description                                        | . 28 |

| 2.3.2 Executable file formats                            | 29   |

| 2.3.3 Kernel and user mode                               | 30   |

| 2.3.4 1/0                                                | . 30 |

| 2.3.5 Context/Thread switches                            | . 31 |

| 2.3.6 Virtual address space                              | . 31 |

| 2.3.7 Demand paging                                      |      |

| 2.3.8 Kernel scalability enhancements                    |      |

| 2.3.9 References                                         |      |

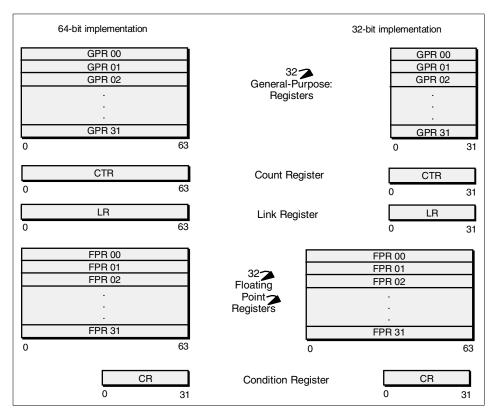

| 2.4 64-bit architecture                                  |      |

| 2.4.1 Concepts                                           | . 33 |

| 2.4.2 Addressability                                     |      |

| 2.4.3 Advantages of 64-bit architecture                  |      |

| 2.4.4 Performance of 64-bit architecture                 |      |

| 2.4.5 Software considerations for 64-bit architecture    |      |

| 2.4.6 64-bit operating system capabilities               |      |

|                                                          |      |

| Chapter 3. IBM RS/6000 and IBM pSeries architectures     |      |

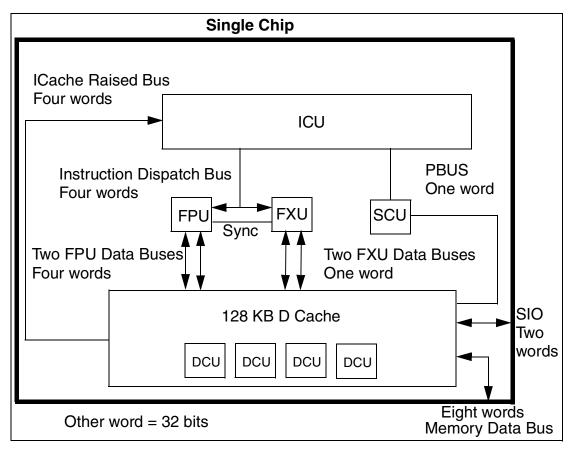

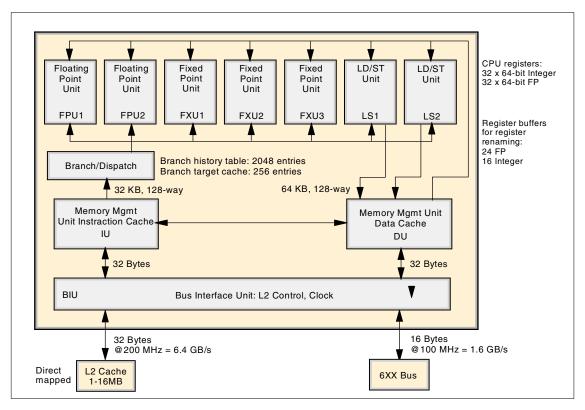

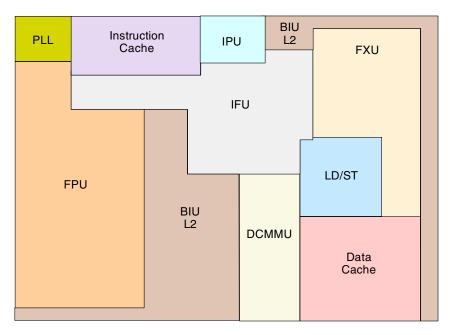

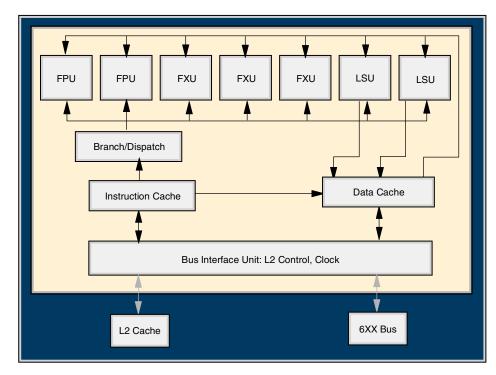

| 3.1 POWER2 Super Chip                                    |      |

| 3.2 POWER3                                               |      |

| 3.2.1 POWER3 execution core                              |      |

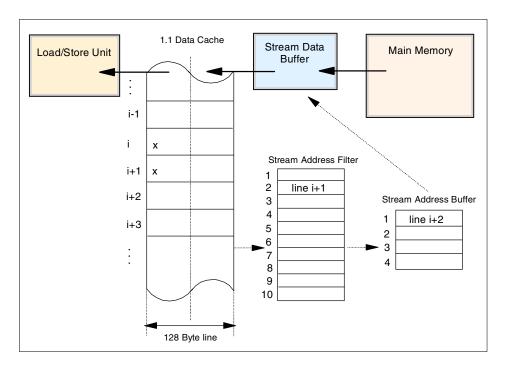

| 3.2.2 Memory access section                              |      |

| 3.2.3 POWER 3 II chip                                    |      |

| 2.2 PowerPC                                              | EΛ   |

© Copyright IBM Corp. 2001

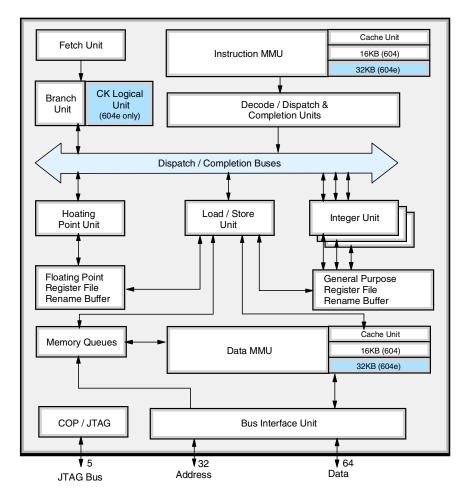

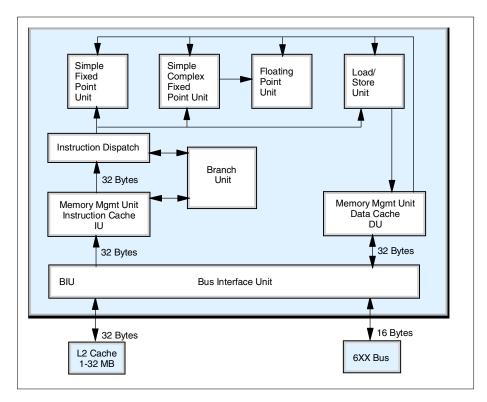

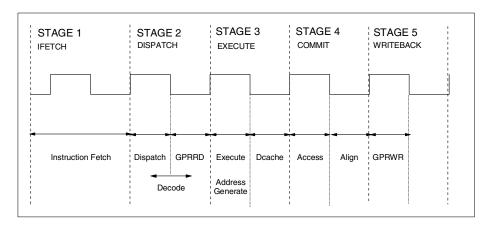

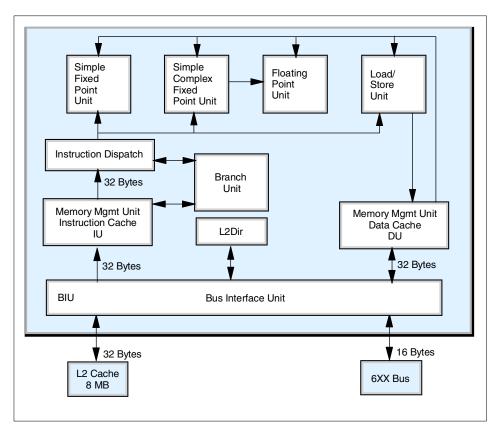

| 3.3.2<br>3.3.3<br>3.3.4 | PowerPC 604 and 604e  Differences between 604 and 604e processors  RS64 II processor  RS64 III processor  POWER4 | 51<br>52<br>60 |

|-------------------------|------------------------------------------------------------------------------------------------------------------|----------------|

| -                       | 4. IBM RS/6000 and IBM pSeries products                                                                          |                |

|                         | metrical Multiprocessor (SMP)                                                                                    |                |

| 4.1.1                   | Migrating to SMP                                                                                                 | 77             |

|                         | Symmetrical Multiprocessor (SMP) concepts and architecture                                                       |                |

|                         | Software                                                                                                         |                |

|                         | Scaling                                                                                                          |                |

|                         | References                                                                                                       |                |

|                         | able POWERparallel (SP)                                                                                          |                |

|                         | Parallel architecture                                                                                            |                |

|                         | IBM SP (Scalable POWERparallel) system                                                                           |                |

|                         | SP switch performance                                                                                            |                |

|                         | Shared disk components of Parallel System Support Program                                                        |                |

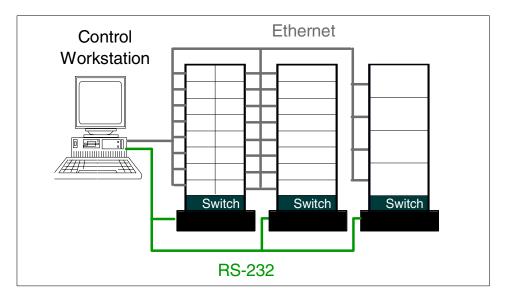

|                         | Sizing and configuring a control workstation                                                                     |                |

|                         | Sizing and configuring an SP system                                                                              |                |

| 4.2.7                   | Resources                                                                                                        | 131            |

| •                       | 5. Hardware                                                                                                      |                |

|                         | essors                                                                                                           |                |

|                         | nory                                                                                                             |                |

|                         | Cache memory                                                                                                     |                |

|                         | Addressing considerations                                                                                        |                |

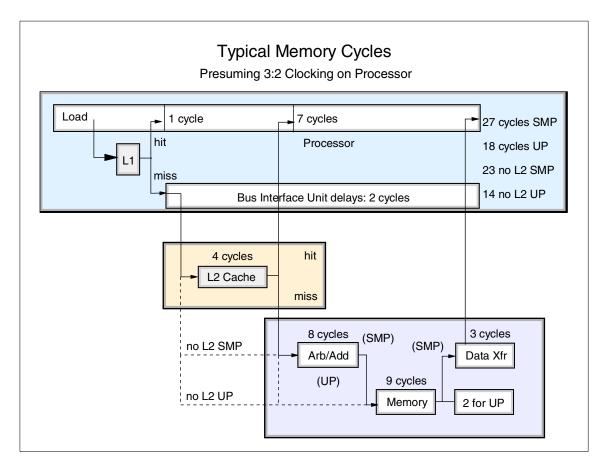

|                         | Memory cycles                                                                                                    |                |

|                         | Uniprocessor vs. symmetric multiprocessor memory cycles $.$                                                      |                |

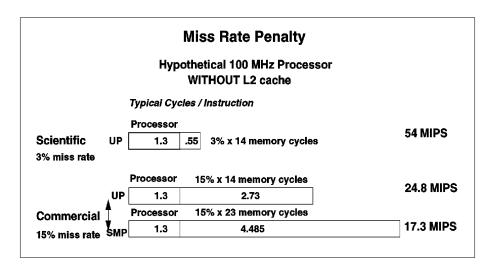

|                         | Miss rate penalty                                                                                                |                |

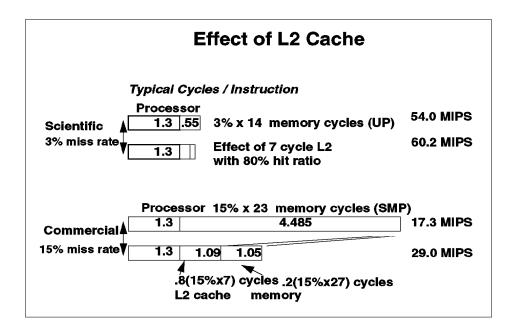

|                         | Effect of L2 cache                                                                                               |                |

|                         | Effect of processor speed                                                                                        |                |

|                         | age                                                                                                              |                |

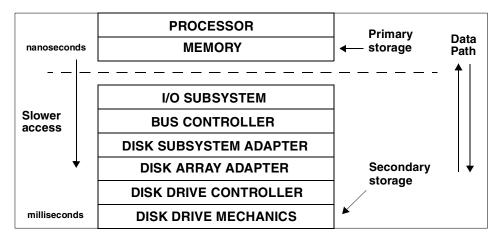

|                         | Performance view                                                                                                 | -              |

|                         | Levels of storage                                                                                                |                |

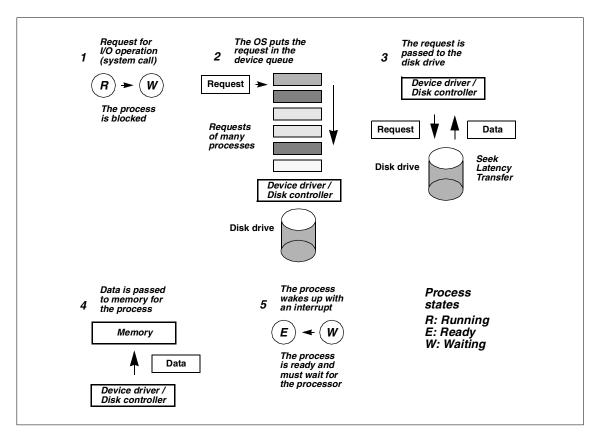

|                         | How an I/O request is processed                                                                                  |                |

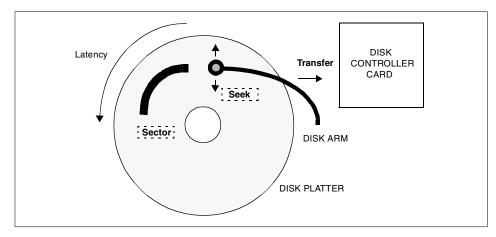

|                         | How a disk works                                                                                                 |                |

|                         | SCSI technology                                                                                                  |                |

|                         | Serial Storage Architecture (SSA)                                                                                |                |

|                         | RAID levels overview and performance considerations                                                              |                |

|                         | IBM Enterprise Storage Server (ESS)                                                                              |                |

| 5.3.9                   | Lawinal Maluma Managay (LMM) as a samta                                                                          | 160            |

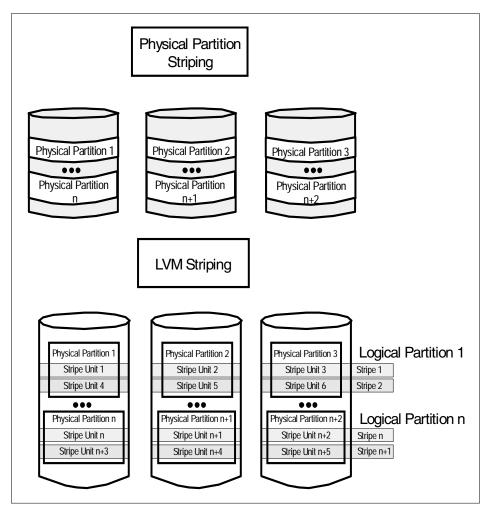

|                         | Logical Volume Manager (LVM) concepts                                                                            |                |

| 5.4 Asyr | nchronous Communication adapters                   | 176  |

|----------|----------------------------------------------------|------|

|          | Terms used in serial communication                 |      |

| 5.4.2    | Flow control                                       | 178  |

| 5.4.3    | Asynchronous adapter overview                      | 179  |

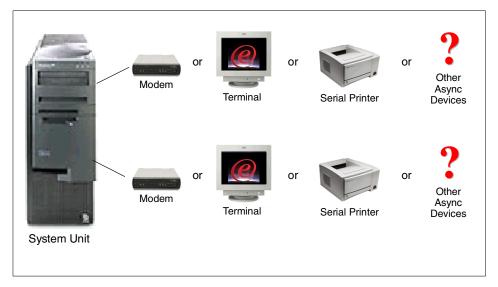

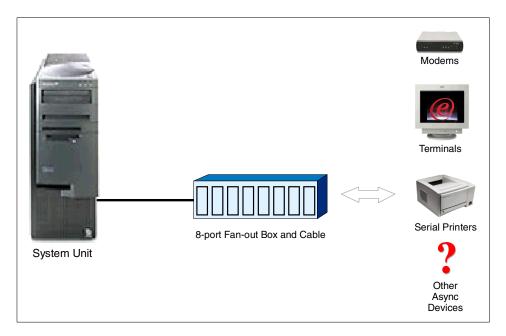

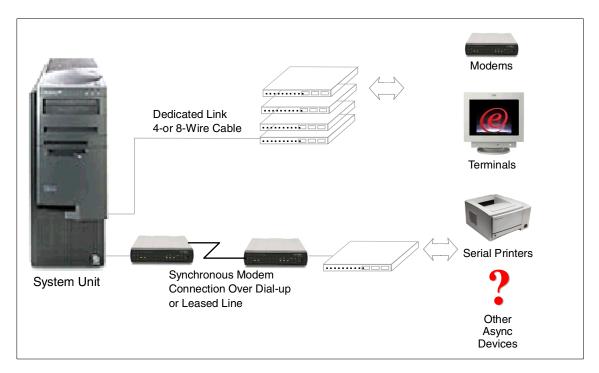

| 5.4.4    | Evaluating asynchronous communications options     | 179  |

| 5.4.5    | Product selection considerations                   | 183  |

| 5.4.6    | Topology considerations                            | 187  |

| 5.5 LAN  | /WAN Adapters                                      | 187  |

|          | Ethernet                                           |      |

|          | Token Ring                                         |      |

|          | Fibre Channel                                      |      |

|          | ATM                                                |      |

|          | General network tuning recommendations             |      |

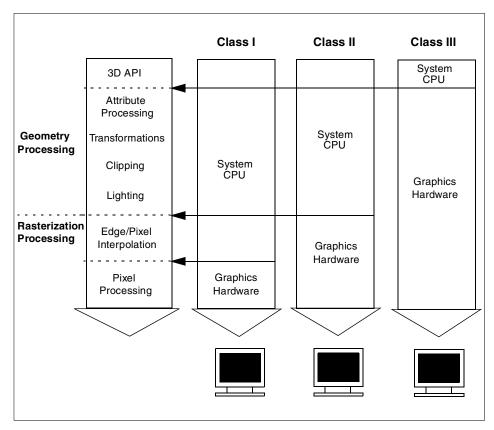

|          | phics accelerators                                 |      |

| 5.6.1    | Currently available RS/6000 graphics accelerators  | 199  |

|          | IBM's graphics workstations                        |      |

|          | Graphics APIs - The "softer side of things"        |      |

| 5.6.4    | Graphics accelerator positioning                   | 205  |

|          | References                                         |      |

|          | vork Station                                       |      |

|          | Network Station memory                             |      |

|          | Boot server performance                            |      |

|          | Boot performance considerations                    |      |

|          | Application performance considerations             |      |

|          | Using CDE with the Network Station                 |      |

| 5.7.6    | Performance summary                                | 212  |

| 01       | C. Barrahanaula                                    | 04.5 |

| •        | 6. Benchmarks                                      |      |

|          | tem Performance Evaluation Corporation (SPEC)      |      |

|          |                                                    |      |

|          | SPEC 5557                                          |      |

|          | SPEC SFS97                                         |      |

|          | Reference                                          |      |

|          | phics Performance Characterization (GPC) Committee |      |

|          | SPECviewperf                                       |      |

|          | saction oriented benchmarks                        |      |

|          | TPC-C                                              |      |

|          | TPC-D                                              |      |

|          | TPC-H                                              | _    |

|          | TPR-R                                              |      |

|          | TPC-W                                              |      |

| 0.3.3    | TD                                                 | 241  |

| 6.5 LINF | PACK                                       | 244 |

|----------|--------------------------------------------|-----|

| 6.5.1    | Metrics                                    | 245 |

| 6.5.2    | Usage                                      | 245 |

|          | Reference                                  |     |

|          | esBench benchmark                          |     |

|          | NotesBench test                            |     |

| 6.6.2    | NotesBench test scenario                   | 249 |

|          | Metrics and how to read them               |     |

|          | Usage                                      |     |

|          | Conclusion                                 |     |

|          | References                                 |     |

| <b>.</b> | - 0                                        |     |

|          | 7. Sizing                                  |     |

|          | eral sizing concepts                       |     |

|          | Guidelines                                 |     |

|          | Concepts                                   |     |

|          | Using AIX Workload Manager (WLM)           |     |

|          | Resources                                  |     |

|          | iuser system sizing                        |     |

|          | Multiuser environment                      |     |

|          | Workload balancing                         |     |

|          | General sizing considerations              |     |

|          | Resources                                  |     |

|          | server sizing                              |     |

|          | NFS sizing                                 |     |

|          | AIX Fast Connect sizing                    |     |

|          | Client/Server sizing                       |     |

| 7.3.4    | General sizing considerations              | 289 |

| 7.3.5    | Resources                                  | 291 |

| 7.4 Data | ιbase sizing                               | 291 |

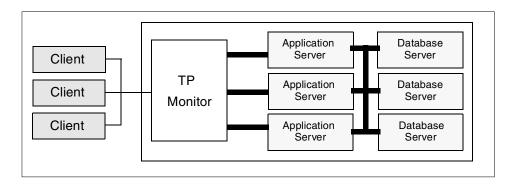

| 7.4.1    | Database environment                       | 291 |

| 7.4.2    | Transaction processing monitor environment | 296 |

| 7.4.3    | Sizing RDBMS                               | 297 |

| 7.4.4    | Resources                                  | 306 |

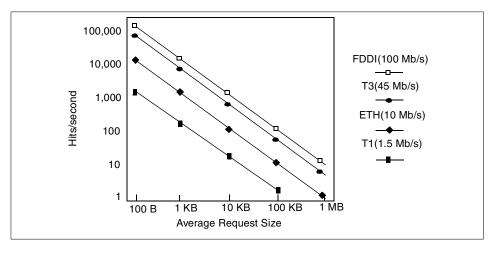

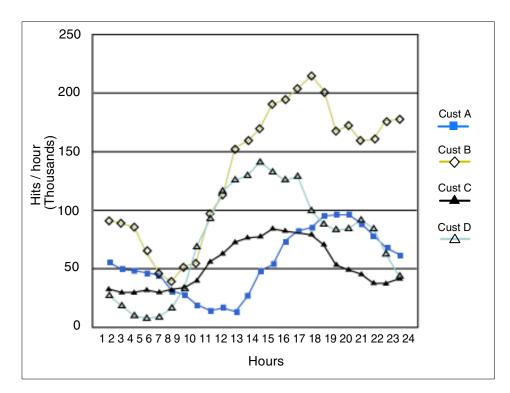

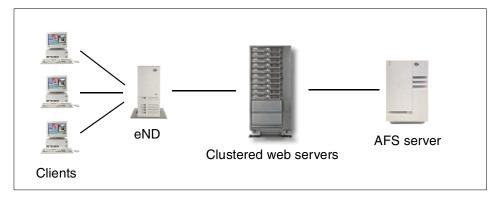

| 7.5 Web  | server sizing                              | 306 |

| 7.5.1    | Introduction                               | 307 |

| 7.5.2    | Sizing preparation                         | 307 |

| 7.5.3    | Sizing factors                             | 308 |

| 7.5.4    | Web server performance                     | 311 |

|          | Sizing IBM HTTP Server                     |     |

|          | Sizing WebSphere Application Server        |     |

|          | Sizing Net.Commerce                        |     |

|          | Resources                                  |     |

| 7.6 Lotu | s Domino Server sizing                         | 325 |

|----------|------------------------------------------------|-----|

| 7.6.1    | Estimate the workload                          | 326 |

| 7.6.2    | Processor sizing                               | 326 |

| 7.6.3    | Memory sizing                                  | 327 |

| 7.6.4    | Disk sizing                                    | 329 |

| 7.6.5    | Example                                        | 329 |

| 7.6.6    | Conclusion                                     | 330 |

| 7.6.7    | Resources                                      | 331 |

| Chapter  | 8. Performance tools                           | 333 |

| 8.1 AIX  | performance tools and commands                 | 333 |

| 8.1.1    | Commands viewed by filesets                    | 334 |

| 8.1.2    | Commands viewed by system resource             | 335 |

| 8.1.3    | Command descriptions                           | 336 |

| 8.1.4    | References                                     | 362 |

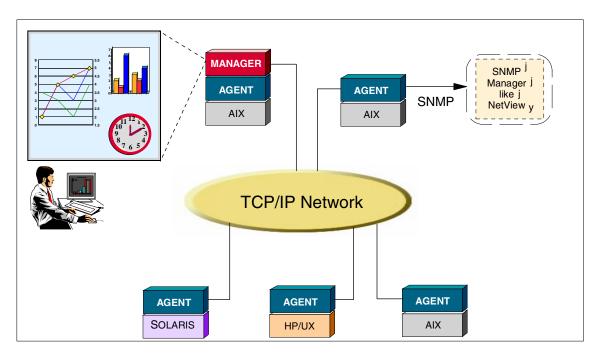

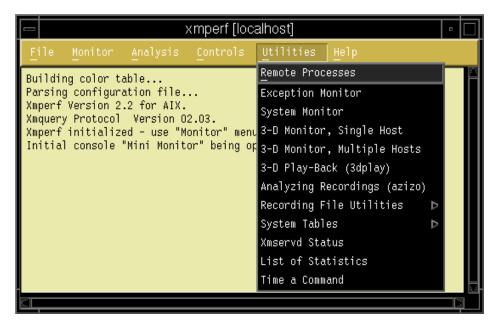

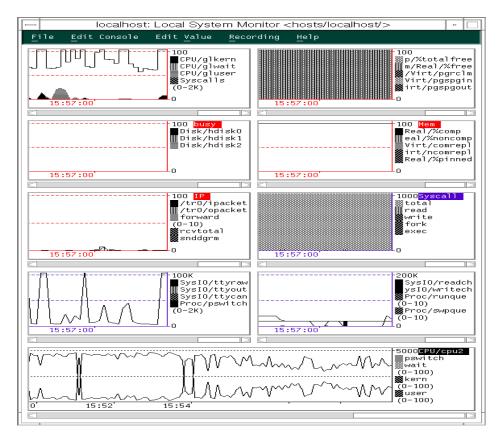

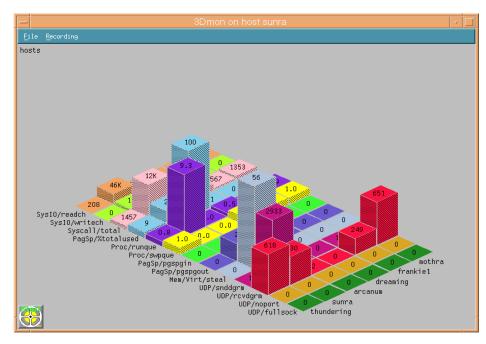

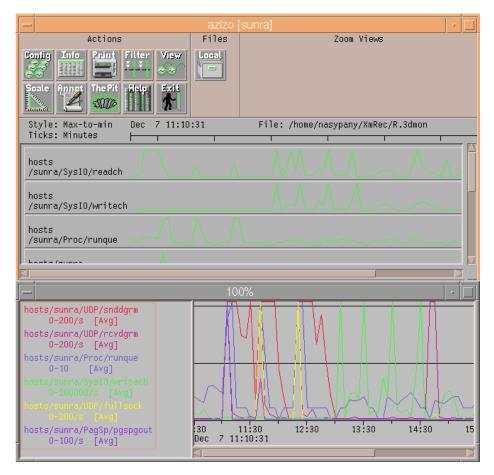

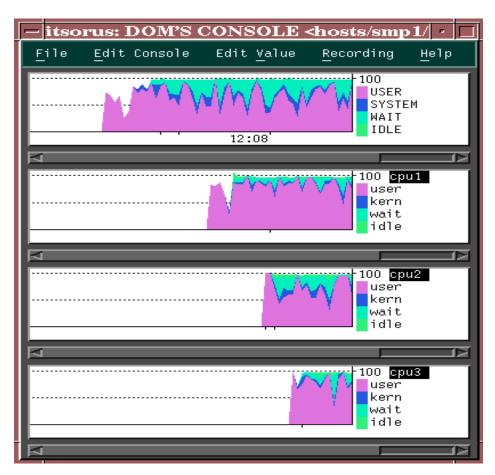

| 8.2 Perf | ormance Toolbox (PTX) for AIX                  | 363 |

| 8.2.1    | Performance Toolbox concepts                   | 363 |

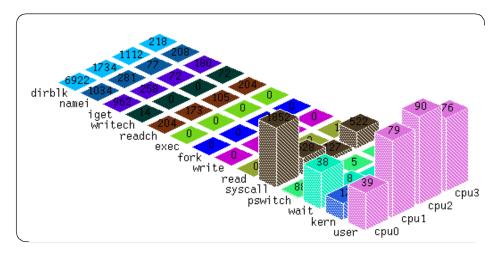

| 8.2.2    | Graphical monitoring and analysis issues       | 365 |

| 8.2.3    | Manager                                        | 366 |

| 8.2.4    | Agent                                          | 372 |

| 8.2.5    | Monitoring an SMP with the performance toolbox | 373 |

| Appendi  | ix A. Special notices                          | 377 |

| Appendi  | ix B. Related publications                     | 381 |

|          | Redbooks publications                          |     |

|          | Redbooks collections                           |     |

|          | er resources                                   |     |

| B.4 Refe | erenced Web sites                              | 381 |

|          | get IBM Redbooks                               |     |

| IBM Red  | books fax order form                           | 384 |

| Abbrevi  | ations and acronyms                            | 385 |

| Index .  |                                                | 391 |

| IDM Dod  | lhooks raviaw                                  | /11 |

#### Preface

Contained in this redbook is a close-up, performance related view of the different hardware architectures IBM offers in its RS/6000 and @server pSeries systems, including system, processor, memory, storage, and network architectures. One chapter is dedicated to general sizing rules for a number of environments such as database sizing, IBM HTTP server sizing, Net.Commerce sizing, and Lotus Domino sizing. The reader will also find a description of the Industry benchmarks that are performed on IBM systems as well as an overview on AIX performance tools.

This redbook is an update to the successful first Edition of "Understanding IBM RS/6000 Performance and Sizing," that was published in 1997. Obsolete information was taken out, still relevant information was updated, and new information was added to this new Edition. While the book was produced, IBM RS/6000 was re-branded to IBM @server pSeries. As a conclusion to that, the given information applies to both brands, even though only one of the brand names might be mentioned, except for the processor and system architectures, which only apply in part to the IBM @server pSeries models.

#### The team that wrote this redbook

This redbook was produced by a team of specialists from around the world working at the International Technical Support Organization Austin Center.

**Diana Gfroerer** is an International Technical Support Specialist for AIX Performance at the International Technical Support Organization Austin Center. She writes extensively and teaches IBM classes worldwide on all areas of AIX Performance and Tuning. Before joining the ITSO in 1999, Diana Gfroerer worked in AIX pre-sales Technical Support in Munich, Germany. She was leading the World Wide Technical Skills Community for AIX and PC Interoperability.

**Nigel Trickett** is a Software Support Specialist at IBM New Zealand. He joined IBM in 1995, working on software calls providing both onsite and telephone support. He has worked with Unix since 1984 and has had several roles since then, including hardware and software support and systems administration. Nigel Trickett's primary responsibilities are to resolve performance issues with AIX and to analyze system dumps. He also works on many types of software issues. Nigel holds a New Zealand Certificate of Computer Technology.

© Copyright IBM Corp. 2001

**Tatsuhiko Nakagawa** is an I/T specialist at IBM Japan. He joined IBM in 1991 and has been working with AIX ever since. He has been working with RS/6000 SP since 1996. He has extensive experience in providing solutions for the banking industries. He has written extensively on sizing methods. He holds a B.S. degree in Electrical Engineering from Waseda University, Tokyo, Japan.

**Ravi Mani** has been working as a Technical Specialist at IBM India Ltd., Bangalore since February, 1996. He has been associated with RS/6000 brand team for more than three years, providing AIX and Hardware support. His responsibilities include benchmarking of various RDBMSs on RS/6000 systems.

Thanks to the following people for their invaluable contributions to this project:

#### **IBM Austin**

Matt Accapadi, Bill Brantley, Bill Britton, Chij-Mehn Chang, DaeSung Chung, Richard Cutler, Herman Dierks, Dixin Gu, Hong Hua, Ernest A. Keenan, Warren Maule, John McCalpin, Andy McLaughlin, Augie Mena III, Stephen Nasypany, Lilian Romero, Joe St Clair, Rakesh Sharma, Tina Tsao, Scott Vetter, Nina Vogl-Wilner

#### **IBM Dallas**

Roger Leukie, John Tesch

#### **IBM France**

Laurent Vanel

#### **IBM Germany**

Dr. Hans-Jürgen Kitzhöfer

#### **IBM Japan**

Jun Nakano, Eiichi Yamamoto

#### **IBM Pougkeepsie**

Ella Buslovich

#### **IBM Rochester**

Karl R. Huppler

#### **IBM San Francisco**

Dale Martin

#### **IBM San Jose**

John Aschoff

#### **IBM Toronto**

Don Bourne

#### **IBM UK**

Nigel Griffiths, Simon Woodcock

#### **IBM Waltham**

Richard Hooker

#### **Comments welcome**

# Your comments are important to us!

We want our Redbooks to be as helpful as possible. Please send us your comments about this or other Redbooks in one of the following ways:

- Fax the evaluation form found in "IBM Redbooks review" on page 411 to the fax number shown on the form.

- Use the online evaluation form found at ibm.com/redbooks

- Send your comments in an Internet note to redbook@us.ibm.com

# Chapter 1. Introduction

Good performance of a system is a relative term because everybody has a different perception of it. It might be defined by:

- The response time for interactive users

- The complete time for batch jobs

- The number of reports finished each day

- The time a system needs for recovery after a failure

- No complaints about poor performance

- The graphical image can be redrawn a certain amount of times every second

- The system never needs changing to fix poor performance

More broadly, a system displays good performance if it meets its performance requirements. Therefore, a clear definition of the performance requirements is mandatory before optimizing system performance, both in business terms (what the users of the system actually see) and technical terms (in quantifiable and measurable numbers).

Good performance is achieved in three phases:

- 1. The system is adequately sized.

- 2. The system is initially set-up to yield the maximum performance from the resources available.

- 3. Regular monitoring and tuning is performed, including upgrading if necessary.

This redbook brings together all the important information that is needed to comprehend IBM RS/6000 and IBM @server pSeries performance and sizing for all three phases.

In this fast changing Information Technology industry, computer design, architecture, configuration rules, and technology are a moving target. It is easy to get left behind as the current state-of-the-art moves endlessly forward. For example, it is now normal to expect high end UNIX systems to include:

- All or a mixture of Symmetric Multi Processing (SMP), Massively Parallel Processing (MPP), and Non-Uniform Memory Access (NUMA) machines

- Level 1, Level 2, and soon Level 3 memory caches

© Copyright IBM Corp. 2001

· Multiple terabytes of disk storage

The above was not true just a few years ago. Also, old theories, unsubstantiated rumors, and myths are often perpetuated due to a lack of in-depth understanding of the latest computing advances. To counteract this, everyone in the IT industry needs to keep up to date and refresh their understanding of the latest trends in computer design and technology. This is a key goal of this redbook, and Chapter 2, "Background" on page 5, Chapter 3, "IBM RS/6000 and IBM pSeries architectures" on page 39, and Chapter 4, "IBM RS/6000 and IBM pSeries products" on page 77 cover these aspects in details.

This redbook will naturally have a wide range of readers with a wide range of backgrounds and needs:

- The system designer and architect. If they understand what is available in the latest range of RS/6000 and IBM @server pSeries machines, they can make early choices in the architecture and design to maximize the cost effectiveness of their solution.

- The technical specialist who is sizing a particular configuration needs to understand how to use the industry standard benchmarks and to compromise costs with performance to achieve a balanced system with upgrade potential.

- The system administrator wishing to maximize the performance of the installed machine, spot real or potential performance bottlenecks and reduce them, or perhaps recommend effective upgrades to maintain performance levels.

- The performance tuning expert who understands generic UNIX

performance tuning concepts and methods, but needs in-depth RS/6000

and IBM @server pSeries specific information to carry out tuning.

- The application or database specialist who needs to understand the underlying platform to ensure maximum performance of their application and that it is efficiently using the resources available.

- Those new to performance and sizing looking for a grounding in the basics of modern computer design, and who need to apply them immediately to the RS/6000 and IBM @server pSeries range.

Although this redbook contains information for all of the above people, they may wish to consult more in-depth redbooks on individual topics. For example, the sizing specialists and system administrators may need specific knowledge of particular RS/6000 and IBM @server pSeries machines that can be found in the RS/6000 and @server pSeries system handbooks, or

those doing performance tuning might want to consult the redbook Performance Tools in Focus, SG24-4989 for more details of the specific tuning tools, their options, and outputs.

When comparing the performance of computer systems it is easy to oversimplify the points of comparison, such as if you compared two fast cars by comparing the official top speeds. The higher the number, the better tuned the car and therefore the faster it will go. However, cars are complex machines, and factors such as brakes, suspension, steering, tires, and regular maintenance and tuning, among many other things, can profoundly affect performance.

When comparing computers it is easy to fall into the same trap - just using one simple measure to determine which is best. For example the MHz rating of the CPUs is a simple measure, but within the RS/6000 there are two models that only differ in the size of the Level 2 memory cache, yet one model is 35 percent faster under a certain workload. Computers are complex machines - just like cars - and it is important to understand that all the components of the computer combine to create good performance. A modern computer needs:

- Fast CPUs

- Fast memory caches

- · High band-width memory controllers and system bus

- Fast memory

- Multi-path I/O channels and disk subsystems

- High throughput networks and rapid graphics

- A robust operating system tuned for the hardware

This is available with RS/6000 and IBM @server pSeries and the AIX operating system, but each part of the system has its part to play in the outstanding performance that these machines make available. This redbook explains each component and how it fits in the overall picture.

For the above reasons, this redbook covers the standard industry benchmarks in some detail so that they can be fully understood and used appropriately. The industry benchmarks, performed by the different hardware vendors, can give a guideline on how a certain hardware system performs under a certain workload. However, it is important to understand two aspects:

• Hardware vendors tune their systems to the extreme levels to achieve top performance numbers for a published benchmark.

Your application will never act exactly the same way as a benchmark application does.

Your best bet is to compare your application workload to the closest benchmark workload as a basis for selecting a hardware system. Chapter 6, "Benchmarks" on page 215 provides an overview on the industry benchmarks that IBM performs on its @server pSeries systems.

In order to size a system, you need to understand the behavior of the application and the workload that it produces. Sizing can only be as good as the information that is available for sizing the system. If there is very little information, then sizing becomes an educated guess as all sorts of assumptions have to be made, introducing inaccuracy. Sometimes application vendors provide sizing recommendations for their applications that can be used to size a suitable hardware system. Otherwise, Chapter 7, "Sizing" on page 255 offers general rules for sizing systems in different environments.

AIX offers a vast amount of performance tools to monitor performance of an IBM RS/6000 or IBM @server pSeries system, including the AIX Performance Toolbox, a graphical performance monitoring tool. Chapter 8, "Performance tools" on page 333 gives a brief overview of the available AIX performance monitoring and tuning tools.

# Chapter 2. Background

The objective of this chapter is to review the major theoretical notions that are useful when considering performance or sizing of RS/6000 machines. For the actual architecture and implementation of the RS/6000, refer to Chapter 3, "IBM RS/6000 and IBM pSeries architectures" on page 39 and Chapter 4, "IBM RS/6000 and IBM pSeries products" on page 77.

Understanding hardware architecture or implementation is important for sizing. For example, you need to understand architectures such as PCI and memory bus of RS/6000 models to size or tune your system.

IBM also offers various system architectures such as SMP, MPP, and NUMA today. These are discussed in this chapter as well as software architectures like the AIX Kernel and Monterey/64.

This chapter does not contain a complete description of hardware architectures and UNIX systems. Only performance-related concepts are presented. If you need to know RS/6000 models in detail, the RS/6000 and pSeries Handbooks are helpful. Go to:

http://www.redbooks.ibm.com/

and search for Handbook in order to get a list of current handbooks.

# 2.1 Performance of processors

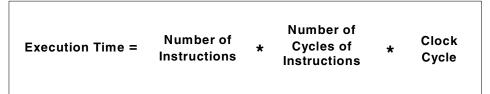

The overall performance of a current processor can be calculated like this:

Figure 1. CPU execution time

The different factors affecting execution time are:

#### Number of instructions

The number of elementary operations needed to complete a program in a result of the compilation. This is called the path length.

© Copyright IBM Corp. 2001 5

#### · Cycles per instruction

This number depends on the complexity of the instructions. The more complicated the instructions are, the higher the number of cycles consumed. But, on the other hand, there are fewer total instructions. This deals with the material discussed in Chapter 2.2.1, "RISC/CISC concepts" on page 6.

# Clock cycle

The smaller the clock cycle, the faster the processor, but the more expensive its production cost.

#### 2.2 Hardware architectures

This section discusses the processor concepts of Complex Instruction-Set Computer (CISC) and Reduced Instruction-Set Computer (RISC), as well as CPU functions that are essential to performance such as pipelining and parallelism. It also examines memory management, including cache and virtual memory concepts.

Further different system architectures, such as the PCI system bus, the different MP concepts, NUMA, and LPAR are discussed.

#### 2.2.1 RISC/CISC concepts

Two different CPU designs have been implemented since the mid-'70s; CISC and RISC.

The first one, complex instruction-set computer (CISC), is the traditional design featuring a large and highly functional instruction set (more than 200 instructions). These instructions need several cycles to complete.

The need for complex instructions existed because, at that time, computers were equipped with small quantities of slow RAM. Complex instructions result in fewer instructions per program, so less memory was needed. But studies showed that only a small percentage of CISC instructions (around 10 percent) were commonly utilized by programs.

Later, as progress in semiconductor technology reduced the difference in speed between memory and processor, and as high-level languages replaced assembly language, the major advantages of CISC decreased.

The reduced instruction-set computer (RISC) concept was first defined by IBM Fellow John Cocke in 1974. It has some basic characteristics:

A very simple architecture with an optimized set of machine instructions.

The instruction set consists only of elementary operations (less than 100 instructions) to reduce the complexity of the instruction decoder. Therefore, the CPU can execute with maximum speed and efficiency. The software generates other, more complex operations by combining several simple machine instructions. All these instructions have a fixed length (necessary for superscalar architecture, as seen later in Chapter 2.2.2, "Superscalar architecture: pipeline and parallelism" on page 7).

· A very high instruction execution rate

The objective of the RISC architecture is to be able to execute an average of one instruction per machine cycle. The execution time can be reduced to less than one instruction per machine cycle using the superscalar architecture, as explained in Chapter 2.2.2, "Superscalar architecture: pipeline and parallelism" on page 7.

Compiler optimization

The performance of the RISC architecture heavily depends on the compiler optimization. The compiler has to be able to exploit the hardware architecture by generating instruction sequences that take advantage of the capabilities and performance of the processor.

Load/store architecture

Memory access is separated from data manipulations in RISC architectures so that the CPU is not stalled by slow memory access. Data is prefetched into registers, and instructions work within those registers, which are the fastest memory available. Working with registers also allows the compiler to better organize data fetching according to data dependency.

In comparison, CISC tries to reduce the number of instructions for a program, whereas RISC tries to reduce the cycles per instruction.

Nowadays, both of these designs have evolved. RISC architectures, which are commonly utilized in the UNIX world, in particular are benefitting from the superscalar concept.

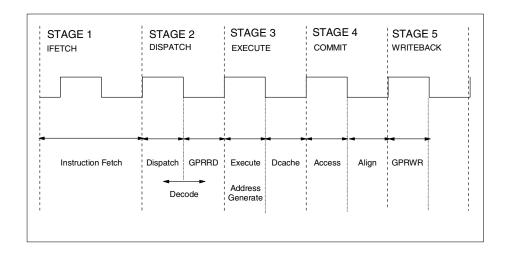

#### 2.2.2 Superscalar architecture: pipeline and parallelism

A pipeline is a hardware feature, similar to an assembly line, designed to increase instruction throughput through internal parallelism. Different units of the CPU perform, in parallel, the various operations required for fetching, decoding, and executing instructions. Several instructions can be executed in the CPU at the same time. The instructions go along the pipeline stages in

synchronization with the CPU clock. This means that, if everything goes well, each time a new instruction enters the pipeline, an older one is exiting. This results in one instruction per pipeline and per cycle. Thus, although the time it takes to complete each instruction is not directly affected, pipelining increases the overall rate at which instructions complete.

When pipelining works as intended, performance is optimized. However, there are some potential problems; branch instructions and data conflicts. A pipeline normally holds a number of instructions in different stages of execution. Consider the case where one of these is a conditional branch, dependent on the condition code to be produced by a not-yet-executed instruction coming through the pipeline. Should it later turn out that the branch is to be taken, the system has to discard all the instructions prefetched after the branch and continue from the branch target address instead. A "bubble" in the pipeline will develop, leading to wasted CPU cycles.

A true data dependency arises when an instruction entering the pipeline needs the result still to be produced by an instruction further ahead in the pipeline. This case cannot be resolved by register renaming, the technique employed to avoid data conflicts. The instruction simply has to wait on the newer one to produce the result.

While true data conflicts are uncommon, branches are frequently encountered. In fact, branch instructions constitute about 20 percent of the instructions in most computer architectures. Branch target prediction as used in the RS/6000 alleviates the problem to a certain degree. The basic problem that remains is that very complex software, like kernel code and database systems, suffers a slowdown of CPU speed in the pipeline because of the high percentage of conditional branch instructions that are typical for these environments. Simpler applications are less affected by this problem.

Next, came the idea of making several pipelines in order to implement further parallelism, which is called superscalar architecture. The instructions had to be distributed between the different pipelines and no more sequential treatment was possible. That is why compilers are so important in the RISC superscalar architecture; complexity no longer lies in the instruction itself but in the compiler. But the advantage of a compiler is its ability to be optimized continuously, quickly, and much more easily than hardware code. Superscalar implies several independent execution units, like branch units, fixed-point units, or floating-point units.

Superscalar allows more than one instruction to complete in a clock cycle. The objective is to achieve the highest number of instructions per cycle.

While the superscalar architecture aims at issuing more than one instruction per cycle, this goal is achieved only when the proper mix of instructions and data is sent through the pipeline. Some benchmarks will perform at several instructions per cycle, but the throughput might go down to less than one in other applications. This has nothing to do with instruction length because the processor can handle the large percentage of floating-point instructions typical of technical and scientific applications. Actually, this instruction mix promotes parallelism because load and store operations and loop counting are handled by the fixed-point unit. The challenge for superscalar, highly pipelined RISC architectures lies in complex commercial applications that use the fixed-point and branch units only. These applications tend to have very short sequential execution paths and poor locality (as discussed in Section 2.2.3.2, "Locality concept" on page 13).

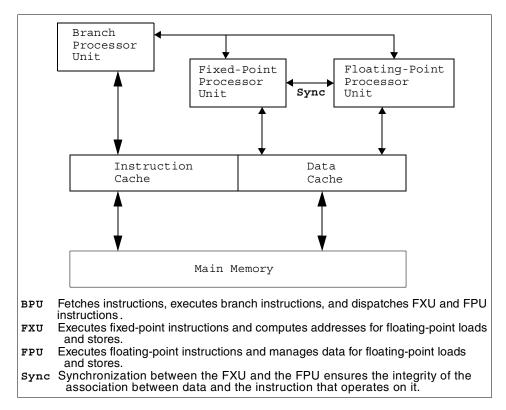

# Simplified scheme of superscalar CPU architecture

Figure 2 on page 10 shows a model of a three-pipelined architecture, the independent processor units being the branch, the fixed-point, and the floating-point processor units.

Figure 2. Pipelined Architecture

# 2.2.2.1 CPU performance enhancements

IBM researchers have announced breakthrough results in developing a new family of experimental high-speed computer circuits that run at test speeds up to five times faster than today's top chips.

The new circuits employ an innovative design - called "Interlocked Pipelined CMOS (IPCMOS)" - to reach speeds of 3.3 - 4.5 billion cycles per second (3.3 - 4.5 GHz) using new copper based transistors while dramatically reducing power consumption. IBM researchers estimate that chips made with IPCMOS circuits would require only half the power used by a standard high-performance chip.

#### 2.2.2.2 Speeding up the clock

The key to the IPCMOS design is a distributed *clock* function. In computer chips, the clock paces the speed of the circuits. Standard designs use a centralized clock to synchronize the operations of an entire chip, ensuring that all operations run at the same interval, or cycle. The clock waits for all the

operations on a chip to finish before starting the next cycle, so the speed of the entire chip is limited to the pace of the slowest operation. To increase the speed, the IBM researchers decentralized the clock, using locally generated clocks to run smaller sections of circuits. This locally generated clock has two significant advantages:

#### • Speed

Faster sections of circuits are free to run at higher cycles without needing to wait for slower operations to catch up.

#### Power

The distributed IPCMOS clocks send signals locally only when an operation is being performed, significantly reducing power requirements where as centralized clocks send a signal to the entire chip. The synchronizing function can use as much as 2/3 of the total power consumed.

#### 2.2.2.3 Reference

Additional information can be located on the web at the following URL:

•http://www.research.ibm.com/news

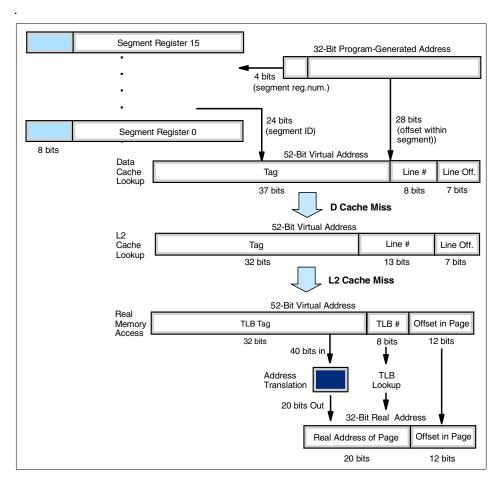

#### 2.2.3 Memory management

Efficient memory management can increase system performance. There are several layers and concepts involved.

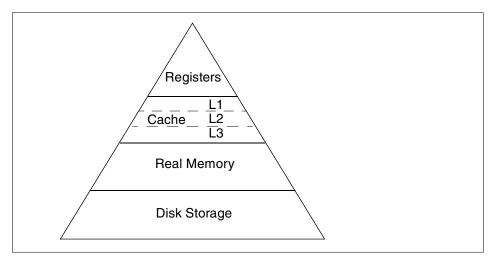

#### 2.2.3.1 Memory hierarchy

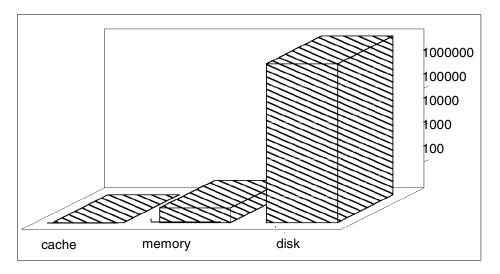

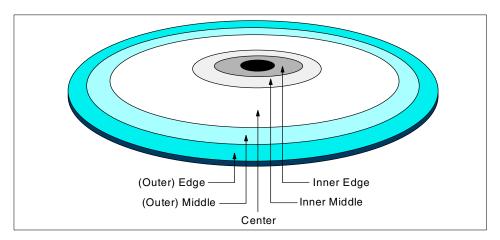

Memory hierarchy is often referred to as having four levels spreading from disk to CPU, but in advanced microprocessor architectures, this scale can be extended to many more levels, including cache levels L2 and L3, which are most common, or a multiple level hierarchy in real memory itself (local memory and remote memory).

Figure 3 on page 12 shows a typical memory hierarchy. At the apex of the pyramid, memory is expensive but the access times are fast, whereas at the base of the pyramid memory is considerably less expensive but the access times are much slower.

Figure 3. Memory Hierarchy

Each level in the pyramid is scarcer and more expensive than the one below.

#### Registers

Registers are storage cells within the specialized units inside the CPU pipelines. This is the fastest memory available, but there are only a few registers. Access is immediate.

#### Cache

Cache is a high-speed memory containing only a subset of main memory. This element is of great importance regarding performance considerations. Indeed, if the CPU accesses the cache instead of main memory for the most-frequently utilized instructions and data, it will gain many clock cycles.

There are usually three different types of cache; levels 1, 2, and 3.

On-chip caches (usually L1, sometimes also L2) are located next to the pipelines, and are the smallest.

Generally, there are one or two cache levels that are off-chip.

L3 cache storage capacity is bigger than that of L2, but its access time is slower. It can be a superset of the L2 cache. When L3 is implemented, L1 cache generally is put on the chip for performance reasons.

#### Real memory

If the data is not in the cache, the data is fetched from main memory.

#### Disk

If the data is not in main memory, a page fault takes place and the data is retrieved from hard disk. This is by far the slowest way to get data.

#### 2.2.3.2 Locality concept

One of the basic principles defining how hardware and software interact is the concept of locality. Hardware expects that programs will exhibit patterns of address reference that are local both in time and space. To put it another way, it is assumed that programs access instructions and data according to the following models:

- Locality in time. This means that, if an address is referenced, it is likely that it will be referenced again soon.

- Locality in space. This implies that, if an address is referenced, it is likely that nearby addresses will also be accessed in the near future.

The principle of locality has given rise to the concept of working sets. The working set of a process is the collection of memory addresses that the process is currently using. This means addresses that the process has recently referenced or is likely to use in the near future. The working set thus comprises those memory ranges that the process needs to have access to without any significant delay in order to achieve maximum performance.

Inherent in the concept of working set is the observation that active address ranges normally do not shift gradually but rather tend to be replaced entirely in phase transitions. Most programs behave so that they remain in one area of memory for some time, then suddenly move to another area, remain there for some time, and so on.

Although locality and working sets are rather vague concepts based on empirical observations rather than strict laws, they are the rationale behind two very powerful architectural features of today's computers; caches and virtual memory.

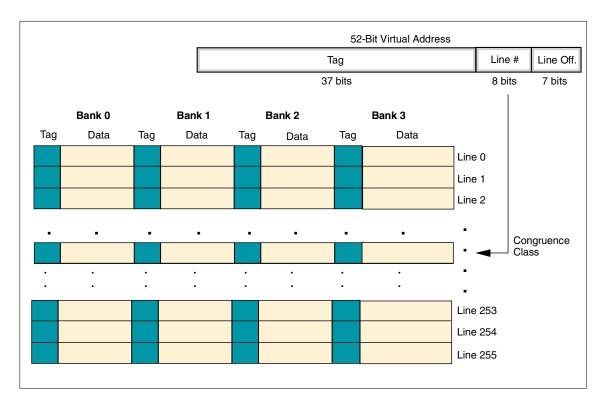

#### 2.2.3.3 Cache

As explained before, cache memory sits between the CPU and main memory.

The L1 cache memory is nowadays typically divided into two sections, one for data (D-cache) and one for instructions (I-cache). In this way, for example, while the arithmetic units work on numeric data in the data cache, the branch processor can simultaneously load new instructions from the instruction cache, which increases parallelism. Lower level caches are normally common caches.

Caches exploit locality on a smaller scale and offer much faster access times than main memory or disk.

Cache can be either integrated within the memory management unit (MMU) or located outside the processor (external cache). Most modern RISC architectures now implement both internal and external caches in order to reduce access to main memory by having a bigger global cache size. In terms of performance, the nearer to the pipelines the cache gets, the smaller the access time is.

#### Data organization

As the cache only contains a subset of main memory data, its data needs to be referenced for the CPU to find it.

Data is organized in lines because too much space would be used to reference each byte otherwise. So each line begins with a tag containing the main memory address of the first byte and some control information like the valid bit. Then comes the real data, made of contiguous words.

When a cache miss happens, the whole line must be fetched from memory because there is only one tag to reference the line.

The line size has some consequences on performance. Indeed, if you choose a small line size like 32 bytes, then a higher percentage of cache space is occupied by tags. This results in a smaller amount of cache, but data transfers between cache and main memory are almost immediate. On the other hand, if you choose a long line size like 128 or 256 bytes, it results in a larger amount of cache available for data, but transfers between main memory and cache are slower because you need to fetch the whole line from main memory. For this kind of implementation, dividing a line into several sublines, each independent and with its own valid bit, may improve transfer time.

#### Hit ratio

Among the various factors influencing performance, one of the most important in determining processor throughput is the cache hit-to-miss ratio. To achieve optimal performance, the CPU needs to achieve a high percentage of cache hits, meaning that the instructions or data required are present in cache memory. If not, the processor will have to wait for the information to be loaded from main memory, which implies a performance degradation of as much as 50 percent. Effectively, while page faults cause either context switches or I/O waits, cache misses actually force the CPU into a wait state, and this forces idling while the requested data or instructions are fetched from memory or, in the worst case, disk.

The CPU wait state is forced because access to real memory is slower than access to the caches by more than an order of magnitude. Furthermore, the RISC architecture and the highly sophisticated pipelines found in the RS/6000 design work at top efficiency only when they can access code and data at a rate of two to four words per CPU cycle.

In addition to the cache hit-to-miss ratio, there is another important factor to be considered; the miss penalty, defined as the number of cycles the CPU must wait while the cache miss is being resolved by the memory subsystem. The cost of a cache miss, in terms of performance, is the product of the cache miss ratio and the miss penalty.

In general, the instruction cache is smaller than the data cache because programs are typically executed in chunks of four to five sequential instructions before the next branch instruction is encountered. Also, the hit rate is usually higher and the average access is faster than for the data cache because the instruction cache is never written to, and the consequences of a cache miss are more severe because the CPU pipelines are immediately stalled.

#### Cache access

The first goal of a cache is to access data faster than memory. Therefore, cache searching must be very quick and efficient.

Generally, it utilizes a hashing algorithm to index the CPU addresses to locations in the cache (except for fully associative caches). Hashing implies that different CPU addresses can have the same index. The cache line tags with this index will then have to be compared to the CPU address to find out if it's a hit or a miss. The hashing algorithm has been chosen because it is an efficient way of limiting the search to only a few lines (the ones that refer to the same index).

Several cache organizations follow:

#### Direct mapped cache

The index refers to only one line of the cache where data may be stored. This is the simplest organization. However, as hashing will produce the same index for many different addresses, it can end up in cache thrashing. This happens when the same lines are continuously replaced by new ones before being reused.

#### n-way set associative cache

This organization is aimed at reducing the probability of cache thrashing. The idea is to group several lines (n) and to refer to them with one index.

Each line is independent of the others in its set and has its own tag. Thus, when the CPU looks for an index, it has just n tags to compare to its own address. These comparisons are made in parallel to avoid reducing performance. Cache thrashing is less likely, as several lines are provided for each index.

#### Fully associative cache

This is a particular case of the preceding organization, when n equals the total number of lines in the cache. It means that there is only one set of lines. So no hashing is implemented. All the lines are looked through in parallel for each search. This is the most expensive cache organization. That explains why it is used only for small caches such as translation lookaside buffers (TLB).

When new data has to come into the cache, some existing line or subline must be put aside. This replacement policy, by which data is selected for removal, is usually done according to the least recently used (LRU) algorithm, which is easier to implement than techniques used for main memory such as page aging.

Another extremely important policy is the update policy. The CPU has to store data. It can do this either to main memory or to cache. If the latter option is chosen, it increases the cache hit ratio because of locality, and the store time is decreased. That is why, in most cases, CPUs store data to cache.

But to ensure data integrity, cache needs to be consistent with main memory. Two options exist. First, write the data both to cache and memory. This is called the write-through policy. The advantage is complete coherency with memory. But it ignores the locality concept and always wastes a memory cycle. The other policy, called the write-back policy, asks the CPU to write only to cache. Data will be written to main memory just before it would be discarded (due to the replacement policy) or if the operating system requests it. Performance enhancement is quite clear, as fewer writes to main memory will occur, but this is done at the expense of main memory consistency. This policy is widely used throughout the different implementations.

#### Performance considerations

- The bigger the cache is, the less main memory will be accessed.

- The write-back policy yields better performance than the write-through policy.

- For small caches, it is generally better to have large sets of lines so that the replacement policy will not induce too much cache thrashing.

Due to spatial locality, the line size should be as large as possible. But very large line sizes will add some overhead when loading lines from memory.

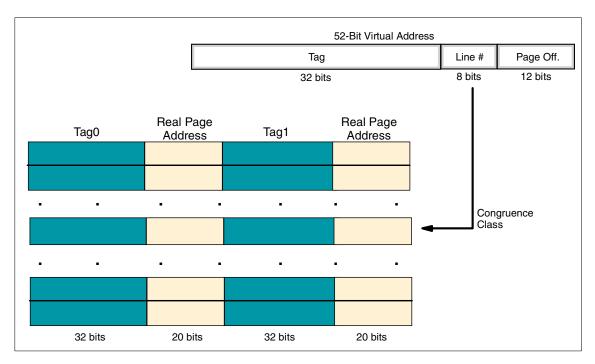

# 2.2.3.4 Virtual memory concepts

Virtual memory has two technical meanings:

- The system can behave as though it has access to more physical memory than actually exists on the system. For example, a 32-bit system is limited to 4 GB of real memory. However, AIX uses a virtual memory manager model that can support as much as 4 PB (4 Petabytes = 4,000 Terabytes) of virtual memory. This is accomplished by implementing a 52-bit virtual address.

- Process text and images are given effective addresses by the compiler, as

opposed to real addresses. Because they have effective addresses, they

can be loaded at any real memory location. Virtual memory allows many

programs to occupy memory at the same time.

#### Swapping

Originally, UNIX systems used a technique called swapping to provide virtual memory. In a swapping environment, entire process images are loaded into real memory. Therefore, when a process is not needed in real memory (such as when it is sleeping), its image is transferred out to a secondary storage device. This secondary storage device is usually a disk partition known as the swap space. This swap space provides a backing store that allows the system to appear to have more physical memory than it actually has. The drawback to swapping is its slow mechanism, as the entire image of the process must be moved from real memory to swap space and back.

#### Paging

A newer virtual memory management technique is paging. In a paging environment, only the most popular pages of a process occupy memory at any given time. A page is a small chunk of code or data that has a fixed size throughout the system. For example, AIX Version 4 uses a 4 KB page size.

Like swapping, paging utilizes a secondary storage device, called the paging space, for backing store. When available real memory space for pages becomes scarce, the system moves the least popular (usually least-recently accessed) pages out of memory to the paging space, making paging completely independent of any process.

There is also a hybrid approach to managing virtual memory. Paging is the standard method, but when real memory becomes overcommitted, the system begins to swap processes. Usually, only sleeping processes will be

swapped out. The swapped out processes must then be put back into real memory before they can be made ready to run. This approach is utilized by AIX Version 4.

#### Performance considerations

When dealing with memory, a couple of issues come up:

- Thrashing: The system spends more time handling page ins and page outs than performing computational tasks. Thrashing occurs when there is so much demand on the real memory that it becomes over-committed. It is a direct result of not having enough real memory to handle the workload. Thrashing is often characterized by a sudden slowdown of system response time and a large amount of disk activity.

- Running out of paging space: If not enough paging space is defined, it

causes the kernel to prevent new processes from starting. The

SIGDANGER signal is sent to most processes in alert. If the condition

persists, the kernel may be forced to terminate processes.

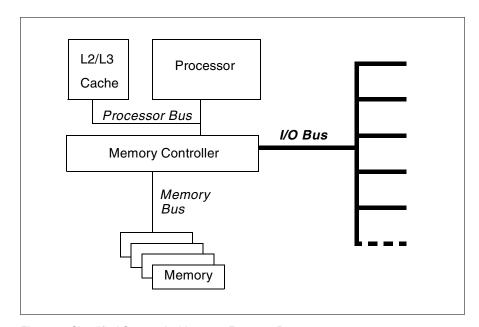

#### I/O buses

So far, we have reviewed notions dealing with the internals of a processor, cache, and memory management. Another performance-related factor that we need to consider is the I/O bus.

Figure 4. Simplified System Architecture: Focus on Buses

#### 2.2.4 PCI

The Peripheral Component Interconnect (PCI) local bus specification was developed by the PCI Special Interest Group (PCI-SIG), led by a group of companies including Compaq, IBM, Intel, Digital, and NCR. Introduced in 1992, the PCI bus architecture has quickly gained widespread industry acceptance.

The goal was to provide a common system-board bus that could be used in personal computers, from laptops to servers. It was envisioned as a local system board bus that would serve as a common design point, supporting different system processors as the various processors evolved over time. This is much like operating systems that have defined Application Binary Interfaces (ABIs) so that applications need not change with each generation of the operating system. The PCI Local Bus would serve as a common hardware interface that would not change with different versions of microprocessors.

The group defined PCI to support the high-performance basic system I/O devices, such as the graphics adapter, hardfile controller, and/or LAN adapter. In the original definition, these would be mounted on the planar and would communicate through the PCI bus. Current I/O buses (ISA, EISA, and Micro Channel) would be used to attach pluggable features to configure the system for the desired use. The first release of PCI Specification was made available in June of 1992.

The PCI Special Interest Group (SIG) soon realized that the PCI bus needed the capability to support connectors. For example, display controller evolution doesn't necessarily match planar development, so providing for an upgrade of the display controller became a requirement. The next release of the PCI Specification (Version 2.0 in April of 1993) included upgrade capability through expansion connectors.

The original design for the PCI bus was to move high bandwidth peripherals closer to the CPU for performance gains. This need for more bandwidth has compelled system vendors to find ways of increasing the throughput of the PCI bus, and the system.

The PCI bus is a clock-synchronous bus that runs at up to 33 MHz for standard operations. It can transfer either 32-bit or 64-bit data. This yields a peak local bus performance of 132 MB/s for 32-bit transfer and 264 MB/s for 64-bit transfer at a clock speed of 33 MHz. PCI allows low-latency random access such that at 33 MHz; as little as 60 nanoseconds are required for a master on the bus to access a slave register.

#### 2.2.4.1 PCI features and benefits

The PCI bus architecture has many advantages involving the following:

- · High data transfer speed

- · Processor independence

- · Cross-platform compatibility

- · Plug and Play

- · Investment protection

#### High data transfer speed

The high-speed data transfer is implemented by the following functions:

· Buffering and asynchronous data transfer

The PCI chip can support the processing and buffering of data and commands sent from the processor or from the peripherals in case the peripheral or the processor is not yet ready to receive the information.

· Burst mode transfer

Variable length linear or toggle mode bursting for both reads and writes improves write-dependant graphics performance.

Caching

To reduce the access time, the PCI bus architecture supports caching of frequently used data.

• DMA

The Direct Memory Access (DMA) function is used to enable peripheral units to read from and write to memory without sending a memory request to the processor. This function is very useful for peripherals that need to receive large amounts of data, such as video adapters, hard disks, and network adapters.

#### Processor independence

Processor independence allows manufacturers to implement PCI buses on any computer. Any PCI-compliant peripheral will work on any PCI-compliant bus implementation.

#### Cross-Platform compatibility

The key to cross-platform compatibility is processor independence. Until PCI, different systems used different buses, such as ISA, EISA, NuBus, and so forth. Now, different systems can use one bus.

#### Multi-bus support

An important aspect to PCI-based system architecture is support for multiple PCI buses, operating transparently to existing software.

#### Plug and play

PCI peripherals, following the PCI standard, load the appropriate set of installation, configuration, and booting information to the host CPU without user intervention. This provides a greater ease of use for the system integrator or end-user.

#### Investment protection

The PCI bus is designed for 64-bit addressing support.

# Summary of I/O Bus Capabilities

Table 1 summarizes the capabilities of the I/O Bus.

Table 1. I/O Bus Capabilities

| Feature                   | Capability |

|---------------------------|------------|

| Data Path Width (bit)     | 32 or 64   |

| Data Bus Speed (MHz)      | 33         |

| Data Transfer Rate (MB/s) | 132 or 264 |

| Data Rate Implemented     | 132        |

#### 2.2.4.2 References

Additional information can be located in the following Redbooks:

- Technical Introduction to PCI-Based RS6000 Servers, SG24-4690

- Understanding IBM RS/6000 Performance and Sizing, SG24-4810

#### 2.2.5 MP implementation specifics

Different types of Multiprocessor (MP) technologies coexist. The three major ones are:

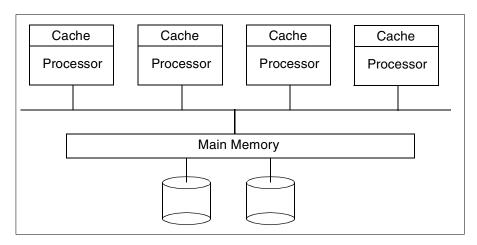

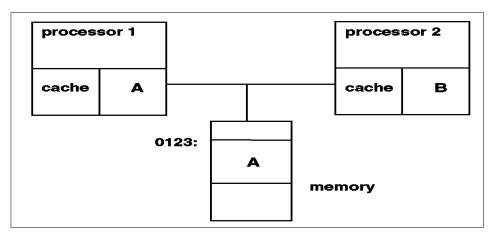

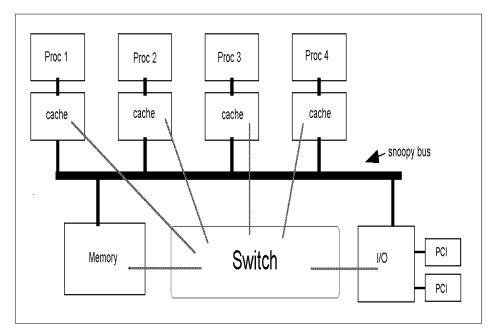

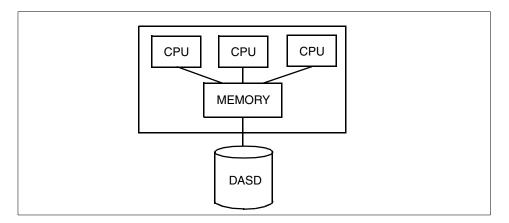

#### Shared Memory MP

A symmetric multiprocessor, also known as a shared memory or tightly coupled MP, has multiple processors that have their own cache and can each address the shared memory and all devices. User processes on any processor see the full machine. If two or more processors access the same word in memory, hardware keeps the caches consistent, invisible to application processes. Compared to other multiprocessor types, the

advantage of SMPs is their use of the same programming model as uniprocessors.

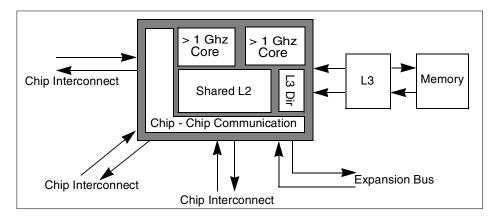

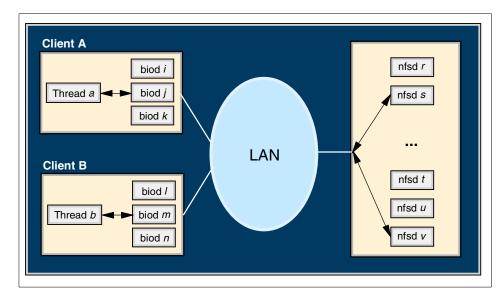

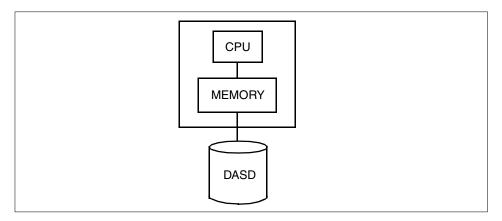

Figure 5. Shared Memory MP

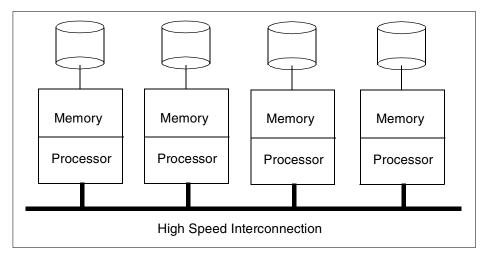

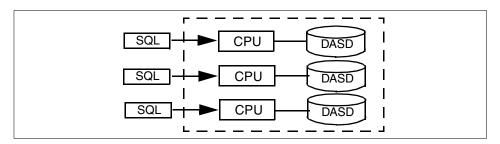

#### Shared Nothing MP

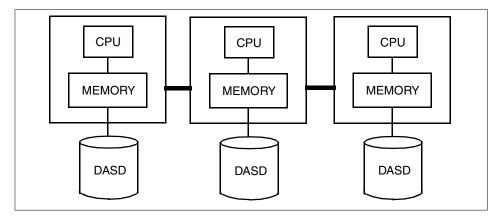

All processors have their own memory and disks. Uniprocessor programs must be changed to use the parallelism of this configuration because they must pass messages across an interconnect in order to use the multiple processors. The IBM RS/6000 SP is an example of this kind of architecture.

Shared nothing MPs generally scale better than SMPs because they have no memory bus contention and no cache coherency problems among the processors.

Figure 6. Shared Nothing MP

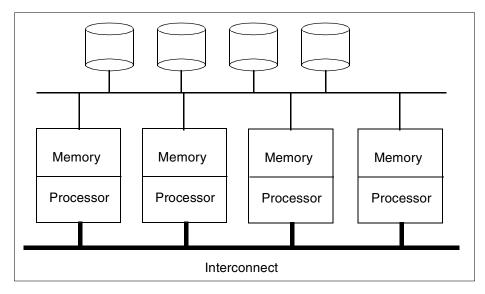

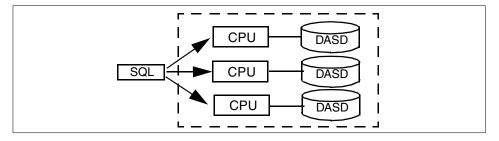

### Shared Disk MP

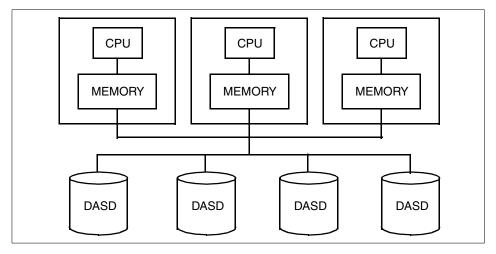

Unlike the SMP, each processor on a shared disk multiprocessor has its own memory. That is why the shared disk multiprocessors, like the shared nothing multiprocessors, have no memory bus contention or cache coherency problems among the processors. However, a centralized locking scheme is used to control access to the disks. This locking scheme requires changes to some applications (such as databases), and generally offsets the performance advantages of no memory bus contention or the cache coherency problem.

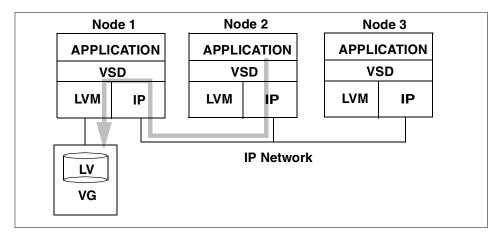

Figure 7. Shared Disk MP

### 2.2.6 NUMA

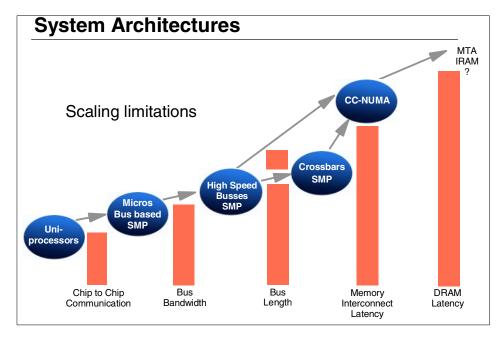

Non-Uniform Memory Access (NUMA) was developed to offer better scalability for large servers. The demand for scalability has increased due to the requirements of large databases and decision support systems such as e-business applications where server load is a key issue.

IBM has done significant work and research on NUMA technology for many years, and when Sequent joined IBM, they brought with them a lot of experience in NUMA performance and tuning.

There has been a steady increase in demand for systems that offer higher CPU power. If the system has performance problems, the logical solution would be to add additional CPU power to the system, but this solution does not address the issues of memory accessing that can quickly erode any performance increases of additional CPU power.

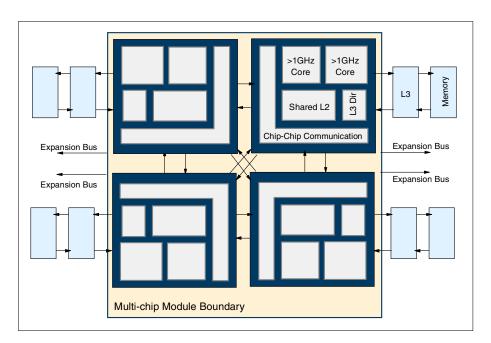

Figure 8 on page 26 shows some of the system components that limit scalability of non-NUMA architectures.

Architecture plays an important role in how a system performs. Architecture must take advantage of the CPU and marketplace technologies and offer scalability. To enhance CPU throughput, the following technologies were developed:

- Symmetrical Multi-Processor (SMP) share everything

- Massively Parallel Processors (MPP) share nothing resource.

There are advantages and disadvantages to both philosophies, and each is suited to different environments. With SMP, the programming model is easier.

MPP provides very high performance for compute-intensive workloads, but requires data partitioning and is therefore not a good choice for running some commercial applications.

With SMP's easy programming model, SMP has been very popular and over time the need for performance of SMP has increased, but with SMP's architectural limitations, you cannot just add CPUs and expect the equivalent gain in performance.

To take advantage of faster CPUs, physically shorter busses and busses with fewer central interconnects are needed to be able to reap the benefits of memory with ever decreasing latency times.

With NUMA, the concept is to combine these areas to offer program simplicity and the flexibility of SMP while providing low-latency, high- multiprocessing for commercial applications.

Software that runs on an SMP system will run on NUMA systems. Some by their nature will even run efficiently, but others will need to understand the NUMA characteristics in order to perform well on a NUMA system. So even if certain software runs well in a large SMP, that is no guarantee it will run well in a NUMA environment.

NUMA combines the resources of a group of systems and allows sharing of data between them. For example, the memory on multiple servers appears as one.

Figure 8. System Architectures

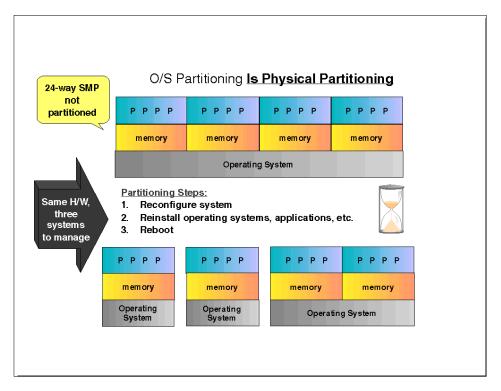

# 2.2.7 Logical partitioning (LPAR)

Logical Partitioning (LPAR) allows the individual allocation of resources (processors, memory, I/O adapters) in any combination and runs a separate operating system on each allocated partition. Each partition can run a different level of operating system. This can be done on SMP systems or NUMA nodes.

Figure 9. LPAR

Each partition has its own memory, processors, and I/O.

Partitioning can be used to solve several problems, like running production and test versions of an application or operating system on different partitions for verification or certification purposes. It can also be used for operating system fault isolation. Also, application failures in one partition do not affect other partitions. It does not protect from global hardware faults, however.

Compared to an unpartitioned system, extra resources are needed due to the fact that each partition requires it's own operating system that has to be managed as an individual system.

Resources may be wasted because the granularity of control is done on hardware boundaries, such as individual processors. Because resources cannot easily be switched from one partition to another, free resources on one partition will be wasted.

A more flexible solution to this problem is provided by various workload management products, such as the AIX Workload Manager (WLM). Detailed information on WLM is available from the redbook *AIX 5L Workload Manager (WLM)*, SG24-5977.

### 2.3 AIX kernel

UNIX is a multiuser and multitasking operating system. The kernel is the core of the operating system.

# 2.3.1 Description

The kernel is a linked object file similar to a user application, and provides the following functions:

- Mechanism for creation and deletion of processes

- CPU scheduling. Because UNIX is a time-sharing operating system, the kernel implements scheduling routines to fairly allocate processor time slices to processes.

- Memory management. The kernel allocates and de-allocates virtual memory for all active processes.

- I/O Handling. The kernel provides the I/O path between applications and the system hardware. I/O support includes device and file I/O. The kernel provides the mechanisms for the creation and management of files via file systems. The UNIX system establishes file names to represent logical and physical devices. These file system abstractions are found, by convention, in the /dev directory. This concept allows applications to access devices for I/O as if they were ordinary files. Thus, the file system provides the application interface for device I/O.

- Handling the loading and execution of programs.

- · Synchronization tools.

- Communications tools for interprocess communication.

The AIX Version 4 kernel is preemptable. A preemptive kernel means that a thread that is running in kernel mode can be interrupted and, upon return from the interrupt, the preempted process can retain control of the CPU.

Other higher priority process can get control of the CPU. AIX Version 4 permits processes to be preempted even if they are in the midst of a system call. Kernel locks are provided to safeguard kernel data integrity.

## 2.3.1.1 The AIX Version 4 kernel is pageable

A pageable kernel means that portions of the kernel can be paged out to paging space. This allows more real memory for applications. Of course, some critical portions of the AIX kernel, such as interrupt handler code and data, are pinned in memory. A pageable kernel means that the system time needed for a system call can vary depending on whether the pages called are in memory or in the paging space.

Most other kernels do not allow the kernel to be paged out, so that the entire kernel must be loaded and pinned into memory, limiting memory availability for other processes. AIX defines kernel extensions as entities added to the base kernel. These extensions can be added to the kernel dynamically, without the need to reboot the system.

### Kernel extensions are:

- · Device drivers

- · System calls

- Virtual file systems (journaled file system, network file system, CD-ROM file system)

- Streams modules (an AT&T creation that facilitates the creation and implementation of character I/O mechanisms)

### 2.3.2 Executable file formats

AIX defines the format of a compiled, executable file as Extended Common Object File Format (XCOFF). XCOFF is based on the AT&T definition of COFF. Programs compiled by the AIX C, C++, Pascal, or Fortran compilers generate XCOFF files. One of the major interests in XCOFF is its ability to dynamically resolve references to shared libraries and other external objects. COFF, on the other hand, can only resolve references statically.

In AIX, the kernel allows the process to share resources simultaneously among many processes and users. Many other, non-UNIX operating systems allow only single access to the machine resources.

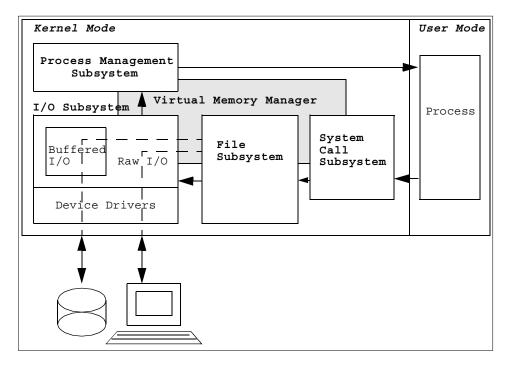

Figure 10. AIX Version 4 Kernel Subsystems

### 2.3.3 Kernel and user mode

When the system is executing user code, it is said to be running in user mode. When the system is executing system calls or other kernel code, such as interrupt handlers in the device drivers, it is said to be running in kernel mode. User applications run in user mode, but if they require the use of a system call, (for example to read or write from disk) this is done in kernel mode. A process in kernel mode cannot be interrupted by the user with a signal to the running process, but it can be preempted.

#### 2.3.4 1/0

Processes access the I/O and process management subsystems via the system call subsystem. The process management subsystem is responsible for scheduling and dispatching processes. The kernel uses two types of interfaces to devices; buffered I/O and raw I/O. Buffered I/O (like hard disk drives or floppy diskette drives) is performed in blocks of data. The blocking factors and schemes used by block devices are controlled by device drivers. Raw devices (such as printers or terminals) perform I/O one character at a

time. The virtual memory manager supports both process management and device and file I/O.

### 2.3.5 Context/Thread switches

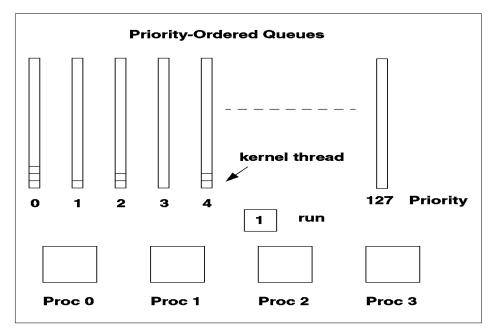

In AIX Version 4, the scheduled entity is the thread (as opposed to process in Version 3). There are 128 levels of priority (0-127). The lower the number, the higher the thread priority. The scheduler recalculates the priorities each second. Each clock tick (time slice), the priority for the currently running thread is recalculated and the dispatcher chooses the thread to run.

A context switch occurs when the execution of the current process is stopped and replaced by the next one (determined by the scheduling policy). The system must store the state and data of the current process and then load those of the next process to be executed. This will slow system performance.

A thread switch is the corresponding action when dealing with threads inside the same process. Because the same process is still executing, less information needs to be safely stored before switching to the next thread. Therefore, this mechanism is much faster than the context switch.

# 2.3.6 Virtual address space

Not to be confused with physical memory (the amount of memory contained in the physical memory chips in the system), the virtual address space is the range of addresses that a process (or the kernel) is allowed to reference.

A 32-bit effective address on AIX is broken into 16 segments, each 256MB in size. The total 32-bit effective address space is therefore 4 gigabytes.

A 64-bit effective address on AIX is broken into 16<sup>23</sup> segments, each 256MB in size. The total 64-bit effective address space is therefore 16 exabytes.

Processes have access to a limited range of virtual addresses given to them by the kernel.

The AIX Virtual Memory Manager (VMM) tries to keep the physical memory as full as possible. By doing so, when a page frame is required there is more chance that it will be in memory. The virtual memory manager keeps track of which pages are clean and which are dirty so the page stealers can obtain memory without paging.

The virtual memory manager can be tuned with AIX's vmtune command. Please refer to the AIX Performance Management Guide for further information.

## 2.3.7 Demand paging

Demand paging occurs when a page is retrieved from either a disk or a page space and is transparent to the user. Demand paging saves much of the overhead of creating new processes because the pages for execution do not have to be loaded unless they are needed. If a process never uses part of its virtual space, valuable physical memory will never be used.

The virtual memory manager can be tuned with AIX's vmtune command. Please refer to the AIX Performance Management Guide for further information.

# 2.3.8 Kernel scalability enhancements

Kernel scalability enhancements have greatly increased OLTP throughput. Because the bigger machines are capable of handling large memory configurations, AIX 4.3.3 supports multiple lists of free memory frames. A frame is a 4 KB unit of real memory. It maps 1:1 to a 4 KB page of virtual memory. The latest kernel also supports multiple page replacement daemons. These constantly-running threads manage real memory by deciding whether the contents of a location in memory should remain where they are or be moved to disk where it will take more time to retrieve them in the future. Allowing multiple lists and having multiple daemons reduces memory contention and latency (the time needed to retrieve data or instructions needed by a processor).

In another kernel enhancement, runnable threads are assigned to local run queues on a per-processor basis. This simplifies the dispatcher's decision about which thread to run next by reducing lock contention and eliminating time-consuming calculations needed to maintain affinity between a processor and its cached data. The algorithms used by the dispatcher have been tuned to provide better transaction throughput on busy SMP systems. At AIX 4.3.3, user threads generate less cache interference and maintain a greater affinity to a single processor.

### 2.3.9 References

Additional information can be located in the following publications:

- AIX 4.3 Kernel Internals Workshop (Course Code Q998C).

- RS/6000 S-Series Enterprise Servers Handbook, SG24-5113

## 2.4 64-bit architecture